机器之心发布

机器之心编辑部

AI 大模型的爆发带动了 GPU 的强劲需求,从云端到边缘渗透的 AI 应用也将带动边缘 AI 服务器及加速处理器的需求。通过对比 GPGPU、FPGA、NPU 和 ASIC,可重构计算架构 CGRA 成为最适合边缘 AI 的并行计算架构。由芯动力提出的可重构并行处理器(RPP)是比传统 CGRA 更适合大规模并行处理的计算架构,这不但通过试验评测得到证实,而且也通过 ISCA 会议得到国际学术权威的认可。基于 RPP 架构的 R8 芯片及后续更高性能的迭代芯片将是边缘 AI 服务器和 AI PC 的理想 AI 加速处理器选择。

目录

一、什么是边缘 AI?

二、边缘 AI 服务器市场趋势

三、适合边缘 AI 的理想计算架构

四、RPP 架构详解

五、RPP 处理器 R8 能效对比

六、RPP 处理器到国际学术权威认可

七、结语

一、什么是边缘 AI?

边缘 AI(AI Edge)是人工智能 (AI) 与边缘计算交叉的先进技术,这一概念源于 AI 从云端向边缘下沉的分布式计算范式转变。边缘 AI 的核心是将 AI 算法直接嵌入到产生大量数据的本地环境中,例如智能手机、物联网设备或本地服务器,通过位于网络 “边缘”(即更靠近数据源)的设备和系统进行实时数据处理和分析。

相对于传统的数据中心或云计算平台的 AI 训练或推理,边缘 AI 的主要优势在于 “就地处理”,大大减少了数据传输和处理的延迟,这在智能监控、自动驾驶、实时医疗诊断或工业自动化控制等应用场景中尤其重要。

实现边缘 AI 计算的设备和系统主要包括:

智能终端:主要用于产生或收集数据的设备,如智能传感器、智能手机、AI PC 或物联网设备等;边缘 AI 服务器:直接对所收集数据进行处理和分析的边缘设备及软硬件系统,比如专用的大语言模型(LLM)AI 推理服务器、智能驾驶区域计算中心服务器等;通信网络设备:尽管边缘 AI 应用对通信网络的带宽和速率要求没有云端那么高,但也必须提供可靠的高速连接才能达到边缘 AI 所需的低延迟和实时性要求。本文主要讨论边缘 AI 服务器及其市场发展趋势、对 AI 加速处理器的要求,以及适合边缘 AI 应用的并行计算架构和处理器实现。

二、边缘 AI 服务器市场趋势

AI 服务器是指专为人工智能应用而设计的高性能计算机设备,能够支持大规模数据处理、模型训练、推理计算等复杂任务。AI 服务器通常配备高性能的处理器、高速内存、大容量高速存储系统,以及高效的散热系统,以满足 AI 算法对计算资源的极高需求。按不同的分类标准,AI 服务器可以大致分为训练服务器、推理服务器、GPU 服务器、FPGA 服务器、CPU 服务器、云端 AI 服务器,以及边缘 AI 服务器等。

据 Gartner 预测,从现在到 2027 年,AI 服务器市场规模将保持高速增长,年复合增长率高达 30%。该机构发布的《2024 年第一季度全球服务器市场报告》显示,今年 Q1 全球服务器市场销售额为 407.5 亿美元,同比增长 59.9%;出货量为 282.0 万台,同比增长 5.9%。在众多 AI 服务器供应商中,浪潮信息蝉联全球第二,中国第一,其服务器出货量在全球市场占比 11.3%,同比增长 50.4%,在 TOP5 厂商中增速第一。

另据中商产业研究院发布的《2024-2029 年中国服务器行业需求预测及发展趋势前瞻报告》,2022 年末,国内市场总规模超过 420 亿元,同比增长约 20%;2023 年约为 490 亿元,市场增速逐步放缓;预计 2024 年市场规模将达 560 亿元。从出货量来看,2022 年中国 AI 服务器市场出货量约 28.4 万台,同比增长约 25.66%;2023 年约为 35.4 万台,预计 2024 年将达到 42.1 万台。

在 AI 大模型发展早期,AI 服务器需求以模型训练为主,因而训练型服务器占据市场主导地位。目前,AI 服务器市场中 57.33%为训练型服务器,推理型服务器占比达 42.67%。然而,随着生成式 AI 应用往边缘端渗透,预计未来推理型服务器将逐渐成为市场主流,边缘 AI 服务器从出货量上将超过云端训练和推理服务器。

IDC 最新发布的《中国半年度边缘计算市场(2023 全年)跟踪》报告数据显示,2023 年中国边缘计算服务器市场继续保持稳步上升,同比增长 29.1%。IDC 预测,到 2028 年,中国边缘计算服务器市场规模将达到 132 亿美元。

作为边缘计算的重要组成部分,2023 年定制边缘服务器规模已达 2.4 亿美元,相较 2022 年增长 16.8%。从厂商销售额角度来看,边缘定制服务器市场中占比较大的厂商分别是浪潮信息、联想、华为、新华三。随着边缘计算应用的多样化发展,新兴服务器厂商在车路协同、边缘 AI 和智能终端等业务场景和应用市场将有较大突破,使得边缘服务器市场呈现出多样化格局。

三、适合边缘 AI 的理想计算架构

PC 时代由 WINTEL(微软 Windows + 英特尔 CPU)联盟主导、智能手机时代由 Android+Arm 联盟主导,AI 时代将由哪个联盟主导呢?一个新的联盟正初露端倪,那就是由英伟达和台积电组成的 NT 联盟(Nvidia+TSMC)。据华尔街投资专家预测,2024 年 NT 联盟总营收预计将达到 2000 亿美元,总净利润 1000 亿美元,总市值有望突破 5 万亿美元。由云端 AI 训练和 AI 大模型应用驱动的英伟达 GPU 和台积电 AI 芯片制造业务将成为今年最大的赢家。

尽管英伟达在云端 AI 训练和推理市场占据了绝对主导地位,但在边缘 AI 应用场景中英伟达的 GPGPU 却不是最佳选择,因为其计算架构固有的高功耗和高成本问题限制了其在更为广泛而分散的边缘 AI 应用中的作用。计算机架构领域的学者专家都在寻求能够替代 GPGPU 的高能效并行技术架构,基于特定域专用架构(DSA)的 ASIC 设计是一种可行的关键思路,比如谷歌的张量处理单元 (TPU) ,这种专为加速机器学习工作负载而设计的处理器采用脉动阵列架构,可高效执行乘法和累加运算,主要面向数据中心应用。另外一个思路是以三星为代表的神经处理单元 (NPU) ,它专为移动场景而设计,具有节能的内积引擎,可利用输入特征图稀疏性来优化深度学习推理的性能。

虽然 TPU 和 NPU 都能够提供部分替代 GPGPU 的高性能和节能解决方案,但它们的专用设计属性限制了其多功能性和广泛的适用性。总部位于美国加州且在台湾和大陆都有研发中心的边缘 AI 芯片初创公司耐能(Kneron)提出了可重构 NPU 的方案,使得 NPU 芯片有 ASIC 高性能而又不牺牲数据密集型算法的可编程性。凭借独特创新的架构和优异的性能,耐能团队获得 IEEE CAS 2021 年 Darlington 最佳论文奖。耐能第 4 代可重构 NPU 可以支持同时运行 CNN 和 Transformer 网络,既可做机器视觉,也可运行语义分析。与仅面向特定应用的普通 AI 模型不同,耐能的可重构人工神经网络(RANN)技术更加灵活,可满足不同应用需求并适应各种计算体系架构。据该公司宣称,其边缘 GPT AI 芯片 KL830 可应用于 AI PC、USB 加速棒和边缘服务器,当与 GPU 配合使用时,NPU 可将设备能耗降低 30%。

可重构硬件是另一种可提供高性能和节能计算的解决方案,现场可编程门阵列 (FPGA) 是可重构硬件计算的代表,其特点是细粒度可重构性。FPGA 利用具有可编程互连的可配置逻辑块来实现自定义计算内核。这种定制的计算能力使得基于 FPGA 的加速器能够部署在金融计算、深度学习和科学仿真等广泛的大规模计算应用中。然而,FPGA 提供的位级可重构性会带来明显的面积和功率额外开销,而且没有规模成本效益,这极大地限制了其在需要低功耗和小尺寸的应用场景中的适用性。

粗粒度可重构架构 (CGRA) 代表另一类可重构硬件。与 FPGA 相比,CGRA 提供粗粒度的可重构性,例如字级可重构功能单元。由于 CGRA 内部的 ALU 模块已经构建完成,且其互联也要比 FPGA 更简单、规模更小,因此其延时和性能要显著好于在门级上进行互连形成组合计算逻辑的 FPGA。CGRA 更适合 word-wise 类型 (32bit 为单位) 的可重构计算,而且可以缓解 FPGA 存在的时序、面积和功率开销问题,是未来边缘 AI 的理想高性能并行计算架构。

下面我们大致梳理一下 CGRA 的发展历程:

早在 1991 年,国际学术界就开启了可重构芯片的研究;2003 年,欧洲宇航防务集团 (EADS) 率先在卫星上采用可重构计算芯片;2004 年,欧洲 IMEC 提出动态可重构结构 ADRES,在三星的生物医疗、高清电视等系列产品中得到应用,日本的瑞萨科技也采用这种架构。2006 年,清华大学微电子所魏少军教授带领的可重构计算团队开始进行可重构计算理论和架构研究;2017 年,美国国防高级研究计划局(DARPA)宣布启动电子复兴计划(Electronics Resurgence Initiative,简称 ERI),将 “可重构计算” 技术列为美国未来 30 年的战略技术之一;2018 年,基于清华大学可重构计算技术的清微智能成立,正式开启商业化进程。2019 年,清微智能量产全球第一款可重构智能语音芯片 TX210,证明了可重构计算的商业价值。2020 年,清微智能获得中国电子学会技术发明一等奖;2023 年,国家大基金二期投资清微智能。目前,清微智能共有边缘端 TX2、TX5 系列芯片,以及用于服务器领域的 TX8 系列三大芯片产品。其中,TX2 和 TX5 系列芯片已应用于智能安防、金融支付、智能穿戴,智能机器人等多个领域;面向云端市场的 TX8 高算力芯片主要应用场景是 AI 大模型的训练和推理。国内另一家基于可重构计算技术的 AI 芯片初创公司珠海芯动力于 2017 年成立,其可重构并行处理器(RPP)架构是改进版的 CGRA。2021 年首颗芯片 RPP-R8 成功流片,2023 年进入金融计算、工业摄像和机器人等边缘 AI 应用市场,并与浪潮信息达成战略合作进入边缘 AI 服务器市场。国际计算机学术界和高科技产业界已形成共识,基于 CGRA 架构的可重构计算芯片具备广泛的通用计算能力,可以应用于各种边缘 AI 计算场景,是解决通用高算力和低功耗需求的必由之路。

四、RPP 处理器架构详解

RPP 和 CGRA 都是属于粗粒度的可重构阵列,都可以达到类似 ASIC 的面积密度和功率效率,而且都是可以用软件编程的。但是,RPP 在可重构类型和编程模型方面跟 CGRA 还是不同的,具体表现为:

1. RPP 是准静态可重构阵列,而传统 CGRA 一般用于动态可重构阵列。静态可重构整列是指每个指令在处理单元(PE)的执行不随时间变化,数据流也是不变的。对于编译器来讲,静态的可重构阵列不需要对指令在时间上进行安排,这样就可以让 RPP 构造更加简单,指令的分配速度很低。因此,RPP 很容易实现一个大型的阵列,譬如 32x32 的阵列。RPP 比传统 CGRA 更加适用于大规模并行计算。

2. RPP 使用的是多线程 SIMT 编程模型,而 CGRA 通常使用的是单线程语言编程。RPP 可以兼容 CUDA 语言,更加适合并行计算。CUDA 语言要求编程人员从一开始就考虑数据的并行度,把并行算法用 CUDA 语言表现出来;编译器则不需要分析并行计算度,编译器就非常简单;CUDA 语言是 SIMT 类型,只用于数据并行的计算,而且并行度在一个程序里保持不变。CGRA 则通常使用 C 语言 + 独立的编译器,虽然理论上可以覆盖任意的计算类型,但是编译器非常复杂,很难达到较高的编译效率。

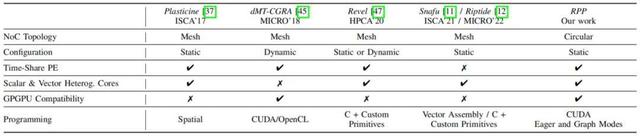

下面图表对 RPP 及几个主流的可重构加速架构做了对比。

RPP 架构的优势可以总结为以下四点:

具有垫片暂存器(gasket memory)的环形可重构并行处理架构,允许在不同数据流之间高效地重用数据;分层式内存设计具有多种数据访问模式、地址映射策略和共享内存模式,可实现高效灵活的内存访问;各种硬件优化机制,如并发内核执行、寄存器拆分和重新填充,以及异构标量和向量计算,从而提高了整体硬件利用率和性能;一个兼容 CUDA 的端到端完整软件栈,具有编译器、运行时环境、高度优化的 RPP 库,可实现边缘 AI 应用的快速高效部署。芯动力基于 RPP 架构提出了 RPP 硬件设计框图,并通过 R8 芯片真实的展现出这种并行计算架构的优越性。这种硬件设计实现主要由一个环形可重构处理器(Circular Reconfigurable Processor)、一个内存单元和一个序列器组成,见下图。

循环可重构处理器是大规模并行计算的核心计算组件。内存单元被分成多个内存组,每个内存组都与一个缓存配对,以利用程序的时间和空间局部性实现高效的数据重用。只有当环形可重构处理器内的寄存器和缓冲区已满时,中间数据才会被传输并存储在内存单元中。序列器用于解码和分发指令到环形可重构处理器,并使用缓存来存储从 DDR 收到的指令。

环形可重构处理器包括 NPU 处理单元 (PE) 和一个垫片内存。每个 PE 都配备了一个内存端口,以方便对内存单元进行数据访问。内存端口设计有模式控制器、地址计算单元和多个多路复用器,以支持不同的数据访问模式和共享内存模式。为了实现灵活的处理器内通信,每个 PE 都集成了一个开关盒 (SB) 和一个互连开关盒 (ICSB),以实现高效的数据转发。这些 PE 按线性顺序连接,垫片内存充当第一个和最后一个 PU 之间的桥梁,从而形成环形拓扑。

环形可重构处理器内的数据处理从第一个 PE 开始,并以流水线方式遍历 PE,中间计算结果按顺序输出到后续 PE。垫片内存缓存最后一个 PE 的输出并将它们重新循环到第一个 PE,从而最大限度地提高数据局部性并消除内存单元的内存流量。PE 中的关键计算组件是处理引擎。在每个 PE 中,都有多个算术逻辑单元 (ALU),其中每个 ALU 都与数据寄存器和地址寄存器耦合。这些数据寄存器聚合在一起形成一个数据缓冲区,便于在每个 PE 内快速访问数据。

此外,线性交换网络和垫片存储器的组合实现了灵活的数据流控制和高效的数据重用,同时消除了传统基于网格的 CGRA 设计中复杂的网络路由。结合对内存单元的灵活高效数据访问,RPP 可以优化数据流处理,最小化内存流量,从而最大限度地提高资源利用效率。

RPP 处理器采用 SIMT 编程模型来为灵活多线程管道启用流式数据流处理。

为了确保与现有 GPGPU 软件生态系统的兼容性,芯动力的 RPP 处理器采用了拥有广泛用户群的 CUDA。CUDA 代码由基于 LLVM 的前端解析,为 RPP 后端生成 PTX 代码。RPP 编译器将 CUDA 内核解释为数据流图并将它们映射到虚拟数据路径(VDP)。然后根据硬件约束将 VDP 分解为多个物理数据路径(PDP),每个 PDP 的配置由序列器在运行时生成。

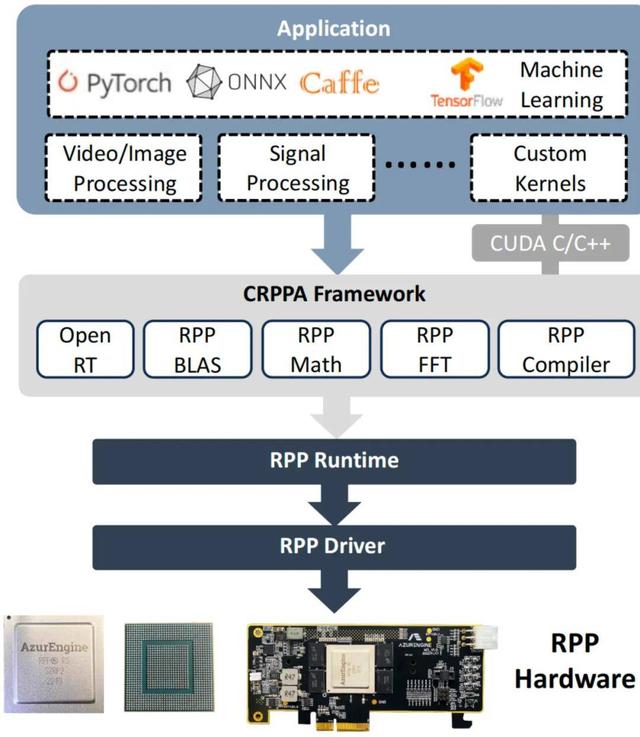

RPP 的软件堆栈可以支持广泛的大规模并行应用,包括机器学习、视频 / 图像处理和信号处理等。对于机器学习应用,该堆栈与不同的主流框架兼容,例如 PyTorch、ONNX、Caffe 和 TensorFlow。此外,用户可以灵活地使用 CUDA 定义他们的自定义程序。这些高级应用程序由 RPP 框架处理,该框架包含一个编译器和不同领域特定的库。在软件堆栈的底部,采用 RPP 运行时环境和 RPP 驱动程序来确保使用工具链编译的程序可以在底层硬件上无缝执行。

五、RPP 处理器 R8 能效对比

基于以上 RPP 处理器硬件设计和完整软件堆栈实现的 RPP-R8 芯片在计算性能和能效上表现如何呢?

R8 芯片的性能参数如下表所示:

针对边缘计算场景,芯动力将 RPP-R8 芯片与两款英伟达边缘 GPU 进行了比较:Jetson Nano 和 Jetson Xavier AGX。Jetson Nano 的芯片尺寸与 RPP 相似,可在物理面积限制内提供相关比较;选择 Jetson Xavier AGX 是基于其与 RPP-R8 相当的理论吞吐量。芯动力在 ResNet-50 推理上评估了这三个 AI 加速平台,其中 Jetson Nano 的吞吐量来自基准测试论文,而 Xavier AGX 的性能数据来自英伟达官方网站。

如上表所示,RPP-R8 的实测运行吞吐量分别是 Jetson Nano 和 Jetson Xavier AGX 的 41.3 倍和 2.3 倍。要知道,Jetson Xavier AGX 的芯片尺寸几乎是 R8 的三倍,工艺也更先进(12 nm vs. 14 nm),但其性能低于 R8。在能效方面,R8 的能效分别是 Jetson Nano 和 Jetson Xavier AGX 的 27.5 倍和 4.6 倍。这些结果表明,在面积和功率预算有限的边缘 AI 场景中,RPP-R8 的表现明显优于 Jetson Nano 和 Jetson Xavier AGX。

深度学习推理是一种广受认可的大规模并行工作负载,也是 RPP-R8 硬件的关键应用。鉴于 Yolo 系列模型与 ResNet-50 等分类模型相比表现出更高的计算复杂度,芯动力选择英伟达 Jeston Nano Orin 作为 GPU 平台,其峰值吞吐量比 Jetson AGX Xavier 更高,为 40 TOPS。由于 CPU 通常不是为高性能深度学习推理而构建的,因此选择 Jetson Xavier Nx 作为比较低端的 GPU 平台,具有 21 TOPS 的峰值吞吐量。评估批处理大小为 1、2 和 4 的工作负载,反映了真实的边缘场景。上图显示了三个平台的吞吐量性能比较,RPP-R8 在 Yolo-v5m 和 Yolo-v7 tiny 上展示了更高的吞吐量。在批量大小为 1 的情况下,RPP-R8 的吞吐量大约比 Jeston Nano Orin 高 1.5× ∼2.5 倍,比 Jeston Xavier Nx 高 2.6× ∼4.3 倍。

评估与测试结果表明,RPP 在延迟、吞吐量和能效方面优于传统的 GPU、CPU 和 DSP 等架构。RPP 处理器的性能提升归功于其独特的硬件特性,主要包括:1) 循环数据流处理:中间结果流经 PE 之间的流水线寄存器和 FIFO,显著减少了数据移动和到远程内存存储的内存流量;与 GPU 和 CPU 中的数据处理相比,这种模式效率更高。2) 分层内存系统:RPP 通过其分层内存系统最大化数据局部性。RPP-R8 芯片面积的很大一部分(约 39.9%)专用于片上存储器。这种设计选择提供了广泛的内存容量,增强了数据重用并减少了频繁访问外部存储器的需求。3) 矢量化和多线程管道:RPP 的硬件架构和编程模型可实现有效的矢量化和多线程管道。这种设计充分利用了 RPP 进行并行处理的全部计算潜力,确保其资源得到最大程度的利用,从而提高性能。

除了在能耗、延迟和吞吐量方面的优势外,RPP 还因其小面积而脱颖而出。只有 119 平方毫米的芯片面积消耗使得 RPP-R8 成为面积受限的边缘计算的理想平台。RPP 的另一个特点是其高可编程性,由全面的端到端软件堆栈支持,可显著提高部署效率。与 CUDA 的兼容性使用户能够利用熟悉的 CUDA 生态系统,从而缩短学习曲线并促进更容易的采用。支持即时编程和图形编程模式,为用户提供了高度的灵活性,满足各种计算需求。包括 OpenRT 和 RPP-BLAS 在内的不同库支持也促进了各种场景中的高性能和高效部署。全栈解决方案,包括硬件架构和软件支持,使 RPP 在各种边缘计算硬件中脱颖而出。

六、RPP 架构得到国际学术权威认可

由芯动力携手英国帝国理工、剑桥大学、清华大学和中山大学等顶尖学府的计算机架构团队共同撰写的论文《Circular Reconfigurable Parallel Processor for Edge Computing》(RPP 芯片架构)已成功被第 51 届计算机体系结构国际研讨会(ISCA 2024)的 Industry Track 收录。芯动力创始人兼 CEO 李原博士与帝国理工博士毕业生 Hongxiang Fan(现在英国剑桥的三星 AI 中心做研究科学家)受邀在阿根廷布宜诺斯艾利斯举行的 ISCA 2024 会议上发表演讲,与 Intel 和 AMD 等国际知名企业的专家同台交流。

本届 ISCA 共收到来自全球 423 篇高质量论文投稿,经过严谨的评审流程,仅有 83 篇论文脱颖而出,总体接收率低至 19.6%。其中,Industry Track 的录取难度尤为突出,接收率仅为 15.3%。

作为计算机体系结构领域的顶级学术盛会,ISCA 由 ACM SIGARCH 与 IEEE TCCA 联合举办。自 1973 年创办以来,一直是推动计算机系统结构领域进步的先锋力量,其广泛的影响力和卓越的贡献使其成为谷歌、英特尔、英伟达等行业巨头竞相展示前沿研究成果的高端平台。ISCA 与 MICRO、HPCA、ASPLOS 并称为四大顶级会议,而 ISCA 更是其中的佼佼者,论文录取率常年保持在 18% 左右。多年来,众多在 ISCA 上发表的研究成果已成为推动半导体和计算机行业发展的关键动力。

本次入选的可重构并行处理器(RPP)论文为边缘计算领域注入了强劲动力。实验结果充分证实,作为一款并行计算的硬件平台,RPP 的性能全面超越当前市场上的 GPU,特别是在对延迟、功耗和体积有着极高要求的应用场景中表现尤为出色。

六、结语

ChatGPT 引爆了 AI 大模型,从而带动了 GPU 和 AI 加速器的巨大需求。AI 应用的发展趋势将从云端 AI 训练和推理逐渐往边缘和端侧 AI 渗透,为各种 AI 应用提供软硬件支持的 AI 服务器也同样遵循从数据中心到边缘计算的分布式扩展趋势。传统 GPGPU 在边缘 AI 应用场景中开始暴露出明显的架构缺陷,其高成本、高功耗和高延迟问题迫使业界专家寻求更为高能效的并行计算架构。

在对比 CPU、GPU、ASIC、FPGA 和 NPU 等不同计算架构后,我们发现可重构计算架构 CGRA 是比较适合边缘 AI 应用的,尤其是芯动力提出的可重构并行处理器(RPP)。通过与英伟达同类 GPU 对比分析,基于 RPP 架构的 R8 芯片在延迟、功耗、面积成本、通用性和快速部署方面都表现出色,我们认为这是目前最理想的边缘 AI 并行计算架构。

在今年 7 月份阿根廷举行的 ISCA2024 学术会议上,关于 RPP 处理器架构的论文得到国际学术权威认可。随着边缘 AI 的发展,AI 服务器和 AI PC 将迎来快速增长的黄金时期,而支持这类边缘 AI 设备的 AI 加速器也将同步增长。由珠海芯动力科技提出的 RPP 处理器芯片也将得到业界认可,成为边缘 AI 应用场景中最为理想的 AI 加速处理器。