一、 核心架构基础从晶体管到功能单元

微处理器本质上是超大规模集成电路(VLSI),由数十亿乃至数百亿个晶体管构成。这些晶体管被组织成具有特定功能的基本单元,比如寄存器就是超高速存储单元,用于临时存放处理器当前直接操作的指令和数据(操作数),其速度远超主内存。然后就是算术逻辑单元 (ALU)用于执行所有算术运算(加、减、乘、除)与逻辑运算(与、或、非、异或)。它是处理器执行实际计算的核心部件。然后是控制单元 (CU)用于指挥整个处理器运作的“大脑”。它从内存获取指令,解码其含义,然后精确控制数据流向寄存器、ALU以及其他功能单元,确保指令按顺序正确执行。它依赖于精确的时钟信号进行同步。

其次还有高速缓存 (Cache)位于处理器核心与主内存之间的高速静态存储器 (SRAM)。它存储处理器近期可能频繁访问的指令和数据副本,显著减少访问速度较慢的主内存所需的时间,是提升系统性能的关键。最后是总线接口单元 (BIU)管理处理器核心与外部系统其他部分(主要是内存和I/O设备)之间的数据通信。

案例比如ARM Cortex-A78是前几年广泛应用于高性能手机处理器(如高通骁龙8系)的核心。其设计高度优化了寄存器访问路径与ALU效率。实测数据显示,在相同工艺节点下,相比前代Cortex-A77,Cortex-A78的整数ALU性能提升约7%,能效比提升高达20%,这对延长智能手机续航至关重要。

二、程序如何驱动硬件的?

软件程序也就是我们说的代码最终体现为存储在内存中的一系列机器指令。处理器执行一条指令可分解为若干关键阶段(指令周期),最核心的就5个,

首先取指 (Fetch)控制单元根据程序计数器(PC)中存储的地址,从内存(或高速缓存)中读取下一条指令。然后译码 (Decode)控制单元解析取回的指令,确定需要执行什么操作(操作码)以及操作数在哪里(寄存器或内存地址)。

接着执行 (Execute)根据译码结果,将操作数送入ALU进行指定的运算,或者执行内存访问(加载/存储数据)。结果可能写回寄存器或内存。

然后访存 (Memory Access - 如有需要),如果指令需要从内存读取数据(Load)或将数据写入内存(Store),则在此阶段执行内存访问操作。

最后写回 (Write Back)即将执行阶段或从内存加载的结果数据写回到目标寄存器中。

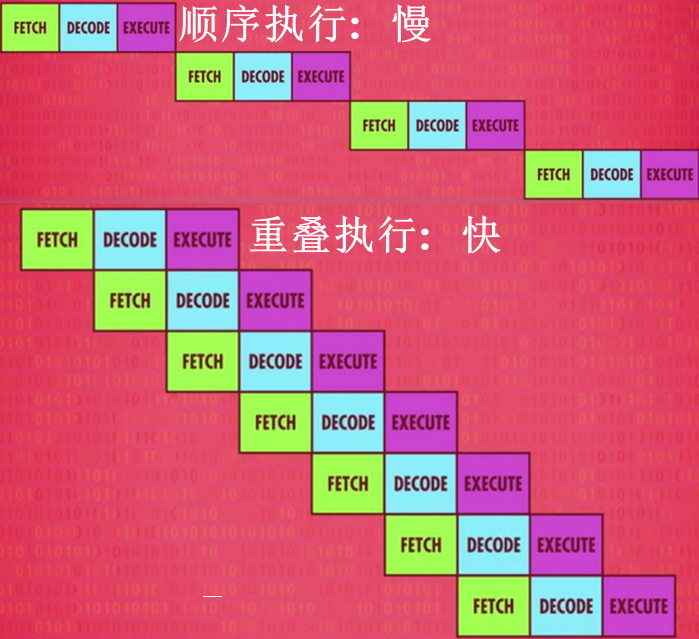

流水线技术作为性能加速器,主要将指令执行过程分解为多个更小的子阶段(如5级、7级、甚至15级以上)。如同工厂流水线,不同指令的不同阶段可以同时重叠执行,极大提高吞吐率。比如Intel Core i7-11800H(Tiger Lake H45)处理器采用复杂超标量架构(每个时钟周期可发射多条指令)与深度流水线设计。其先进的分支预测器通过分析历史分支模式,能极高精度地预测分支方向,大幅减少控制冲突带来的性能损失。实测在SPECint_rate基准测试中,其分支预测错误率通常低于5%,显著提升了代码执行效率。

三、 性能与功耗P/P的平衡艺术

在目前更广泛应用的电池供电的电子设备中,性能与功耗的平衡是核心挑战,或者说相比于孱弱的电池续航能力,处理器的性能是过剩的。现代微处理器采用多种关键技术,来解决此问题

比如多核架构,即将多个独立的处理器核心集成在同一芯片上,实现真正的并行处理。主要是同构多核,这种很简单就是所有核心相同(如4个Cortex-A78)。但实际上另一种用得更多,更普遍,也就是异构多核 (big.LITTLE),组合高性能大核(处理繁重任务)与高能效小核(处理后台轻负载任务),这是现代手机SoC的标配。实现的哲学就是深度考虑性能和功耗平衡的关系,高性能需求场景,比如游戏,4K视频场景就开高性能核心;而不用,idle, 桌面场景,等情况就开高能效的核心,省电省功耗。

还有一大杀器是动态电压频率调整 (DVFS)。根据当前计算负载,实时动态调整处理器的运行电压和时钟频率。负载低时,大幅降频降压以节省功耗。

另一大杀器是时钟门控CG与电源门控PG. 通过精确控制时钟信号只发送给当前活跃的功能模块(时钟门控);彻底切断空闲功能模块的电源供应(电源门控),几乎消除其静态功耗。

最后是专用硬件加速器。是一种间接的处理逻辑,原理是集成针对特定任务的专用电路(如NPU用于AI推理、GPU用于图形渲染、ISP用于图像处理、DSP用于音频处理)。这些硬件单元执行特定任务的效率远高于通用CPU核心,且功耗更低。

举个例子,比如苹果A14仿生芯片iPhone 12系列展示了高性能与高能效的典范。其包含:

·2个高性能Firestorm大核(运行频率高达3.1GHz)

·4个高能效Icestorm小核

·4核GPU

·16核神经引擎(NPU)

表: 苹果A14仿生芯片核心配置与能效亮点

四、 设计实践与趋势分析

设计调试主要还是关注最核心的部分,首先是理解总线协议如熟练掌握AXI、AHB、APB等片上总线协议,是调试处理器与内存、外设间通信问题的关键。逻辑分析仪和总线协议分析仪必不可少。其次是善用调试接口如JTAG、SWD、CoreSight(ARM)等调试接口是连接处理器内部状态的桥梁。熟练使用GDB/LLDB结合OpenOCD等工具进行源码级调试、寄存器查看、断点设置。功耗是重点,如功耗分析与优化,可利用电源分析仪测量芯片不同模块、不同工作状态下的实时电流电压。结合OS电源管理框架(如Linux的CPUFreq、CPUIDle),优化DVFS策略、任务调度和休眠唤醒流程。以及重点关注热管理,因为处理器发热直接影响性能和可靠性。设计有效的散热方案(散热片、热管、风扇、导热材料)并监控核心温度,触发必要的降频保护机制。

新兴趋势也有三点值得特别关注,是未来3-5年的热门方向。首先是很火的RISC-V的崛起,开源免费的RISC-V指令集架构正迅速获得消费电子领域青睐,尤其在IoT、可穿戴设备、定制加速器领域,核心能提供前所未有的设计自由度和成本控制潜力。

其次还有最近很火的Chiplet与先进封装,主要是光刻机制程工艺收益越来越低,而将大型SoC拆分成更小的、功能独立的Chiplet(如CPU Chiplet、I/O Chiplet、AI加速Chiplet),通过先进封装技术(如台积电CoWoS、InFO)集成在一起。这提升了良率、降低了复杂芯片的开发风险和成本,并支持混合不同工艺节点的Chiplet以优化性能和成本。

最后是无处不在的AI, 使得专用NPU正从高端手机向中低端设备、甚至MCU渗透,用于实现设备端实时语音识别、图像处理、预测性维护等智能化功能。关注INT4/INT8量化、模型压缩等边缘AI优化技术,以及AI芯片设计,制造,优化等都是非常好的方向。

案例SiFive Performance P550。RISC-V处理器IP供应商SiFive推出的Performance P550核心,在12nm工艺下主频可达2.4GHz以上,SPECint2006测试成绩超过8.65/GHz,性能接近ARM Cortex-A75水平。其可定制性吸引了包括英特尔在内的巨头探索在消费领域(如AI加速卡、异构计算)的应用。这为工程师提供了除ARM之外的强大新选择。

总结

微处理器是现代消费电子产品的智能心脏。从基础的寄存器、ALU、控制单元协同运作,到复杂的流水线、多核架构、异构计算与功耗管理技术,其内部世界充满了精妙的工程智慧。对于消费电子工程师而言,深入理解这些原理不仅是调试复杂问题的基石,更是设计创新的源泉。把握RISC-V的开放机遇、Chiplet的灵活潜力等前沿方向,将帮助我们在未来几年的设计中占据先机。