1. Preamble与Postamble的定义与作用

Preamble是在数据传输开始前的一段预同步信号,用于建立DQS与DQ的同步关系。

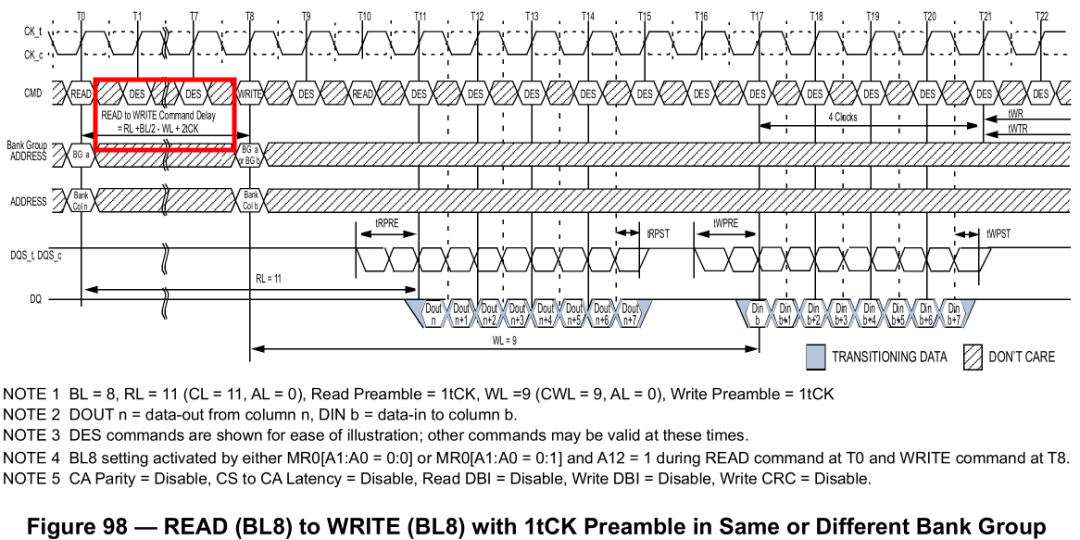

进一步可以分为读操作Read Preamble,是DQS在数据有效前进入预同步状态,提示控制器数据即将到来。读Preamble可配置为1 tCK或2 tCK,通过模式寄存器(MR4[A11])选择。以及写操作Write Preamble,是DQS在写入数据前启动预同步,通常为1 tCK或2 tCK(由MR4[A12]配置)。选择2 tCK时需调整CWL(CAS写延迟)参数。

而Postamble则指在数据传输结束后的一段缓冲信号,用于稳定信号并避免采样错误。

读/写Postamble一般在DDR4标准中读Postamble固定为0.5 tCK,写Postamble也为0.5 tCK。但部分LPDDR4实现支持扩展(如1.5 tCK),lpddr4相关的章节有详细的表述。

preamble:从DQS第一个有效沿(上升沿)开始计算

postamble:从DQS最后一个有效沿(下降沿)开始计算

2. 硬件设计中的配置要点

首先对于模式寄存器(MR)配置中,在读Preamble模式,一般通过MR4[A11]选择1 tCK或2 tCK。若启用2 tCK模式,需结合读均衡(Read Leveling)训练优化时序。

而在写Preamble模式中,通过MR4[A12]选择1 tCK或2 tCK。2 tCK模式需将CWL增加1个周期。

而Postamble扩展中分场景可通过MR1或MR3调整Postamble长度(如0.5 tCK或1.5 tCK),但DDR4标准中通常固定为0.5 tCK,前文已有提及。

对于时序参数调整而言主要是CWL(CAS Write Latency),在2 tCK写Preamble模式下需增加CWL值(具体根据速度等级)。

还有tWTR(Write to Read Delay) 和 tWR(Write Recovery Time),在2 tCK写Preamble需额外增加1个周期。

3. 调试与验证关键点

调试和验证的关键点主要有三个方面,首先是信号完整性分析,需要保证DQS与DQ相位对齐,主要是Preamble为DLL(延迟锁相环)锁定提供时间窗口,需确保DQS与DQ的相位差为90°以优化采样眼图。而Postamble侧重于缓冲作用,主要是避免因总线寄生参数或ODT(片上终端电阻)切换导致的信号振铃(Ringing)。

其次是测试与验证方向,比如时序参数测试中使用示波器验证tRPRE(读Preamble时间)、tWPRE(写Preamble时间)、tRPST(读Postamble时间)等是否符合规范。同时注意VL(参考电平)设置,JESD规范与测试工具可能存在差异。

而在Read Preamble训练中,在MPR(多用途寄存器)模式下启用训练,优化读均衡并校准DQS窗口。

最后是PCB设计优化,主要的关键点如阻抗匹配与串扰控制,需要注意设计中缩短DQS与DQ走线长度差,减少反射和串扰。另外一部分是电源滤波的处理,为DDR4电源网络添加高频去耦电容,降低噪声对时序的影响。

4. 实际应用场景

首先在无缝连续读写中,当命令间隔满足tCCD(CAS到CAS延迟)= BL/2时,可省略Preamble与Postamble,利用前一笔操作的Postamble作为后一笔的Preamble,提升效率。

其次是高频率设计中,在DDR4-3200等高速模式下,需优先选择2 tCK Preamble以预留足够的同步时间。

右上图可以看出,非连续的两组数据,preamble需要重新发送。

总结

Preamble和Postamble是DDR4时序设计的核心机制,需通过模式寄存器灵活配置,并结合信号完整性分析和时序验证确保系统稳定性。调试时需重点关注DQS/DQ相位关系、寄存器配置一致性及测试规范差异,以应对高速场景下的挑战。