Micro LED-CPO(共封装光学)被业界视为AI算力时代突破“功耗墙”与“带宽墙”的终极方案之一。然而,这项技术的商业化之路并非坦途,其核心瓶颈在于封装环节。Micro LED-CPO的封装并非显示级Micro LED技术的简单延伸,而是一场融合了光电、半导体与精密制造的异质集成革命,其技术难点贯穿了从芯片到系统的全链条。

芯片级难点:从“显示”到“通信”的根本性跨越

芯片级难点:从“显示”到“通信”的根本性跨越用于光通信的Micro LED与用于显示的Micro LED在底层要求上存在巨大差异,这直接导致了芯片制造和处理的复杂性。

材料与波长的不匹配:显示用Micro LED主要采用GaN基蓝光芯片,而光通信需要850nm、1310nm等特定红外波段。这要求采用InP(磷化铟)等完全不同的材料体系,使得晶圆异质集成的难度大幅提升。高频驱动与热管理:光通信要求单通道50GHz以上的调制带宽,而显示级产品普遍在10GHz以内。在如此高的频率下,InP基Micro LED的结温攀升速度比显示级快3倍,带来了严峻的散热挑战。巨量转移的精度与良率:将数百万甚至上亿颗微米级LED芯片从生长基板转移到驱动电路基板上,这一“巨量转移”过程要求极高的精度和效率。任何微小的偏差都会导致良率下降和成本飙升。 封装级难点:纳米级的精度与可靠性挑战

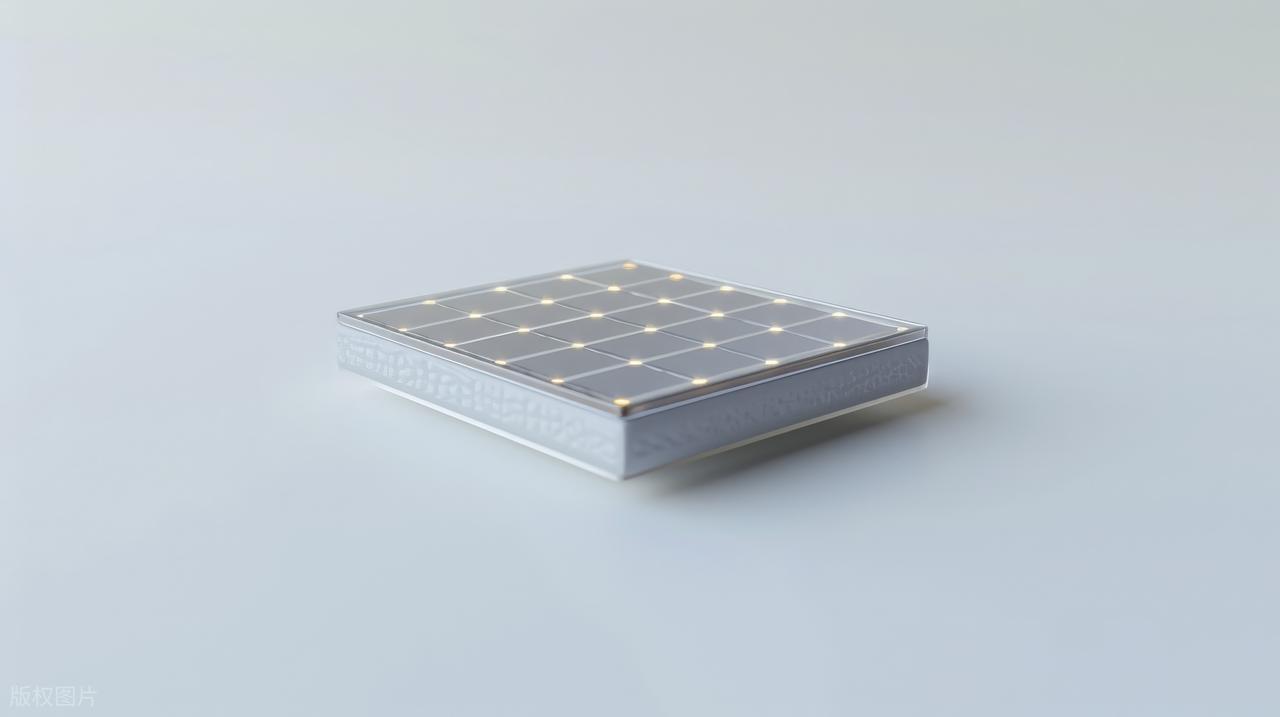

封装级难点:纳米级的精度与可靠性挑战将Micro LED光源与硅光芯片、交换芯片(ASIC)共封装,是整个方案中最关键的环节,也面临最严苛的工程挑战。

纳米级光耦合对准:Micro LED发出的光需要高效耦合进光波导或光纤中,这要求耦合精度控制在±1~2微米以内。一旦超出这个范围,耦合效率损失可能超过30%,导致信号传输失败。异质材料热膨胀失配:CPO封装内集成了硅光芯片(CTE≈2.6 ppm/K)、有机基板(CTE≈15-17 ppm/K)等多种材料。在温度变化时,不同材料膨胀收缩程度不一,会产生巨大的机械应力,可能导致焊点疲劳、光路偏移,最终影响器件的长期可靠性。极端热流密度管理:光电芯片高密度集成导致局部热流密度激增至500-1000 W/cm²,远超传统封装的散热极限。如何在如此狭小的空间内有效散热,防止芯片过热导致性能下降或损坏,是封装设计的核心难题。 产业化难点:成本、标准与生态的制约

产业化难点:成本、标准与生态的制约除了技术本身,从实验室走向大规模量产还面临着产业化的重重障碍。

高昂的制造成本:无论是Micro LED芯片本身,还是高精度的异质集成封装工艺,都导致当前成本居高不下,限制了其大规模商用。缺乏统一标准:CPO涉及芯片、光器件、封装、系统等多个环节,目前产业链上下游缺乏统一的互操作标准,影响了不同厂商产品的兼容性和规模化部署。可靠性验证不足:数据中心要求光器件在高温高湿、长期满负荷下稳定运行超过25年。Micro LED-CPO作为一种全新架构,其在复杂环境下的长期可靠性仍需时间和大量实测数据来验证。综上所述,Micro LED-CPO的封装技术难点是一个系统性工程,涵盖了从材料、工艺到设计的方方面面。尽管挑战重重,但其在功耗和带宽上的颠覆性优势,正驱动着全球科技巨头和产业链企业持续投入研发。随着技术的不断突破,Micro LED-CPO有望在2027年后逐步迈入规模化商用阶段,成为AI算力基础设施的关键一环。