半导体培训6:光刻工艺

撰写:李星

引言

半导体光刻技术是集成电路制造过程中的核心技术,被誉为微电子制造的"心脏"。随着集成电路向更高集成度、更小特征尺寸方向发展,光刻技术的重要性日益凸显。本报告将全面阐述半导体光刻技术的起源、发展、前沿技术、材料、工艺流程、关键参数、质检标准、工装治具、设备以及主要供应商等,为新兴国家半导体产业的发展提供系统的技术指导。

半导体光刻技术的起源

半导体光刻技术的起源可以追溯到20世纪50年代,与晶体管的发明密切相关。1947年,贝尔实验室发明了第一只点接触晶体管,这标志着光刻技术的萌芽。1958年,美国德克萨斯仪器公司(TI)成功试制了世界上第一块平面集成电路,这被认为是光刻技术正式诞生的标志。

1959年,世界上第一台晶体管计算机诞生,进一步推动了光刻工艺的发展。仙童半导体公司(Fairchild)研制出了世界上第一个适用单结构硅晶片,开创了现代半导体制造的先河。

1961年,美国GCA推出了第一台接触式光刻机,这标志着光刻技术正式进入工业化应用阶段。经过60多年的发展,光刻技术不断突破极限,使得微电子技术以前所未有的速度发展。

半导体光刻技术的发展

早期光刻技术(20世纪50-70年代)

在光刻技术发展的早期阶段(20世纪50-60年代),半导体芯片制造商主要使用可见光作为光源。这一时期的光刻技术相对简单,主要采用接触式或接近式光刻方法,将掩模直接接触或靠近涂有光刻胶的硅片,通过可见光曝光形成图案。

20世纪60年代,仙童半导体公司提出了CMOS集成电路制造工艺,这进一步推动了光刻技术的发展。这一时期,光刻技术主要用于制造早期的集成电路,特征尺寸较大,通常在微米级别。

紫外光刻时代(20世纪70-80年代)

到了20世纪70-80年代,光刻技术开始采用汞灯产生的紫外线作为光源。这一时期主要使用G线(436纳米)和I线(365纳米)作为光源,这些波长的紫外线能够提供更高的分辨率,使特征尺寸减小到亚微米级别。

这一时期的光刻技术发展迅速,特征尺寸不断减小,从20世纪60年代的数百微米缩小到20世纪80年代的亚微米级别。光刻技术的分辨率提高使集成电路的集成度显著增加,推动了微电子技术的快速发展。

深紫外光刻时代(20世纪90年代-2000年代)

20世纪90年代至21世纪初,光刻技术开始采用深紫外(DUV)光源。这一时期主要使用KrF(248纳米)和ArF(193纳米)作为光源,这些波长的深紫外光能够提供更高的分辨率,使特征尺寸进一步减小到纳米级别。

这一时期的光刻技术面临诸多挑战,包括光源稳定性、光刻胶敏感性、对准精度等问题。为了解决这些问题,研究人员开发了多种技术,如离轴照明、相位掩模、双重图案化等分辨率增强技术(RAT),以提高光刻的分辨率和图案转移的准确性。

极紫外光刻时代(21世纪10年代至今)

21世纪10年代以来,极紫外(EUV)光刻技术逐渐成为主流。EUV光刻使用13.5纳米波长的光源,能够实现7纳米及以下的工艺节点。EUV光刻技术的出现使集成电路制造进入了一个新的时代,特征尺寸不断突破物理极限。

EUV光刻机的光源产生方式非常复杂,采用激光等离子体型光源,即利用高功率的激光击打金属锡,产生高温高密度的等离子体,辐射出极紫外光。这种技术虽然早在多年前就被证实,但直到最近才克服了技术难题,实现了商业化应用。

随着EUV光刻技术的发展,光刻技术继续向更高分辨率、更小特征尺寸方向发展,为集成电路技术的持续进步提供了坚实基础。如今,光刻技术已经将集成电路制造线宽从40多年前的2~3微米缩小到先进的10~15纳米,创造了人类科技史上的奇迹。

光刻机工作原理

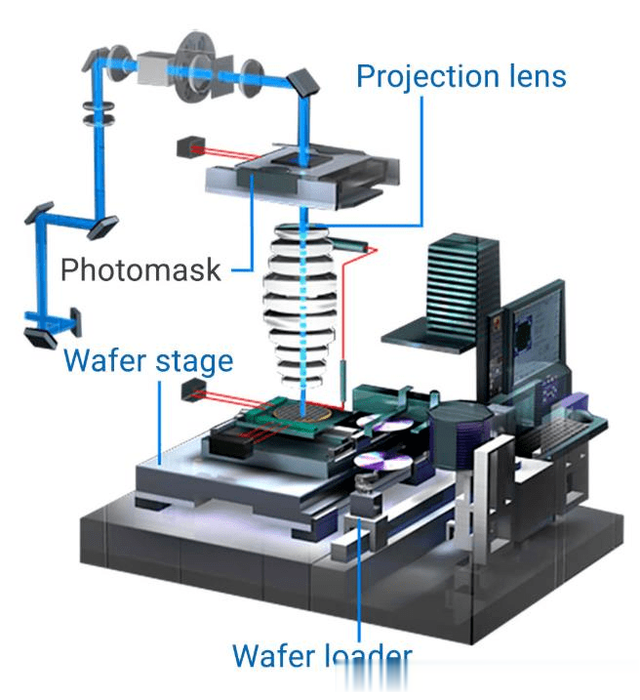

光刻机基本结构

光刻机是半导体制造过程中最关键的设备之一,其基本结构包括光源系统、光路系统、掩模系统、投影物镜系统、工作台系统和控制系统等部分。光源系统产生高能量的光束,光路系统将光束引导到掩模上,掩模系统承载着需要转移的电路图案,投影物镜系统将掩模上的图案缩小并聚焦到硅晶圆上,工作台系统则负责精确控制硅晶圆的位置,控制系统协调各部分的工作,确保光刻过程的精确性。

曝光原理

光刻机的工作原理基于光的曝光。在光刻过程中,光通过掩模上的图案被投射到涂有光刻胶的硅晶圆上。光刻胶是一种对光敏感的材料,当它暴露在光线下时会发生化学反应。未被掩模阻挡的光区域会使光刻胶溶解,而被掩模阻挡的区域则保持不变。这样,掩模上的图案就被转移到了硅晶圆上。

投影物镜系统

投影物镜系统是光刻机的核心部分,它负责将掩模上的图案缩小并聚焦到硅晶圆上。现代光刻机的投影物镜系统通常使用折射式或反射式光学系统。折射式光学系统使用透镜将光束聚焦,而反射式光学系统则使用镜子将光束聚焦。反射式光学系统在高数值孔径和高分辨率方面具有优势,因此在先进制程中更为常见。

工作台系统

工作台系统在光刻机中起着至关重要的作用。它负责精确控制硅晶圆的位置,确保光刻图案能够准确地转移到硅晶圆上。工作台系统通常包括真空吸附系统、位置控制系统和温度控制系统等。真空吸附系统用于固定硅晶圆,位置控制系统用于精确控制硅晶圆的位置,温度控制系统则用于控制硅晶圆的温度,以减少热膨胀对光刻精度的影响。

控制系统

控制系统是光刻机的"大脑",它负责协调各部分的工作,确保光刻过程的精确性。控制系统通常包括计算机控制系统、软件控制系统和硬件控制系统等。计算机控制系统用于处理复杂的光刻数据和算法,软件控制系统用于实现光刻过程的自动化,硬件控制系统则用于控制光刻机的各个硬件设备。

曝光过程

光刻机的曝光过程通常包括对准、曝光和对准调整等步骤。首先,工作台系统将硅晶圆固定在正确的位置,并通过位置控制系统确保硅晶圆的位置精确。然后,控制系统启动光源系统,产生高能量的光束。光束通过光路系统被引导到掩模上,掩模上的图案将光束阻挡或透射,形成特定的光图案。接着,投影物镜系统将光图案缩小并聚焦到硅晶圆上,完成曝光过程。最后,控制系统根据反馈信息调整对准,确保光刻图案的精确性。

光源系统

光源系统是光刻机的能量来源,它产生高能量的光束,为光刻过程提供能量。现代光刻机的光源系统通常使用准分子激光器、同步辐射光源或电子束等。准分子激光器是一种气体激光器,能够产生高能量的紫外线光束,非常适合用于光刻。同步辐射光源则是一种高强度的X射线光源,具有极高的亮度和准直性,适用于高精度的光刻。电子束则是一种非光子束,可以通过扫描方式实现高分辨率的光刻。

光路系统

光路系统在光刻机中起着引导和控制光束的作用。它通常包括一系列的光学元件,如反射镜、透镜、光阑等。这些光学元件能够精确地控制光束的路径、强度和方向,确保光束能够准确地投射到掩模上。光路系统的设计和优化是光刻机性能的关键因素之一。

掩模系统

掩模系统是光刻机的关键部分之一,它承载着需要转移的电路图案。掩模通常由石英玻璃制成,上面涂有金属层或抗反射层。掩模上的图案是通过电子束直写或光刻工艺制作的,具有极高的精度和分辨率。在光刻过程中,掩模被放置在光路中,光束通过掩模上的图案被阻挡或透射,形成特定的光图案。

对准系统

对准系统在光刻机中起着至关重要的作用,它确保光刻图案能够准确地转移到硅晶圆上。对准系统通常包括光学对准和电子束对准两种方式。光学对准利用光学原理,通过观察掩模和硅晶圆上的标记来实现对准。电子束对准则利用电子束的高分辨率特性,通过扫描硅晶圆来实现高精度的对准。对准系统的精度直接影响光刻的精度和良率[11]。

真空系统

真空系统在光刻机中起着重要的作用,它为光刻过程提供一个无尘、无振动的环境。真空系统通常包括机械泵、分子泵和真空腔等部分。机械泵用于抽除空气,分子泵则用于进一步降低真空度。真空腔则用于容纳硅晶圆和光学元件,确保它们在高真空环境下工作。真空系统的性能直接影响光刻的精度和稳定性。

冷却系统

冷却系统在光刻机中起着至关重要的作用,它确保光刻机在高功率运行时不会过热。冷却系统通常包括水冷系统和风冷系统两种方式。水冷系统通过循环冷却水来吸收热量,而风冷系统则通过风扇吹动空气来带走热量。冷却系统的性能直接影响光刻机的稳定性和寿命。

电气系统

电气系统是光刻机的动力来源,它为光刻机的各种设备和系统提供电力。电气系统通常包括电源、配电系统和控制系统等部分。电源为光刻机提供稳定的电压和电流,配电系统则将电力分配到各个设备和系统。控制系统则负责协调各部分的工作,确保光刻过程的精确性。

软件系统

软件系统在光刻机中起着至关重要的作用,它控制和协调光刻机的各种操作。软件系统通常包括操作系统、应用软件和控制软件等部分。操作系统为光刻机提供基本的运行环境,应用软件则用于实现具体的光刻功能,如图案设计、曝光控制等。控制软件则负责协调各硬件设备的工作,确保光刻过程的精确性。

维护与保养

光刻机的维护与保养是确保其长期稳定运行的关键。定期的维护和保养可以及时发现和解决潜在的问题,延长光刻机的使用寿命。维护和保养通常包括清洁光学元件、检查真空系统、校准对准系统等。此外,定期的软件更新和升级也是维护和保养的重要部分,可以确保光刻机的性能和功能始终处于最佳状态。

半导体光刻技术的发展历程

早期光刻技术

20世纪50年代末至60年代,半导体光刻技术处于萌芽阶段,主要采用接触式光刻和接近式光刻技术。接触式光刻是将掩模直接压在涂有光刻胶的晶圆上,通过紫外灯照射使光刻胶曝光。这种方法简单但容易导致掩模和晶圆损坏,且分辨率有限。接近式光刻则将掩模与晶圆保持一定距离,通过光学系统成像,提高了分辨率但仍然存在对准困难的问题。

光刻技术的突破

1963年,斯坦福大学的威廉·博伊尔和乔治·史密斯发明了电荷耦合器件(CCD),这一发明推动了光刻技术的发展。1965年,英特尔的戈登·摩尔提出了著名的"摩尔定律",预测集成电路上可容纳的晶体管数量每18-24个月翻一番,这一定律成为了推动光刻技术不断进步的动力。

光刻技术的商业化

20世纪70年代,随着半导体产业的快速发展,光刻技术开始走向商业化。1972年,美国GCA公司推出了第一台商用步进重复光刻机,采用汞灯作为光源,分辨率为4μm。1978年,日本尼康公司推出了NGL-300D步进重复光刻机,分辨率为1.5μm,标志着日本在光刻技术领域的崛起。

光刻技术的成熟

20世纪80年代至90年代,光刻技术迅速成熟。1982年,美国KLA公司推出第一台自动缺陷检查系统,提高了光刻质量控制水平。1984年,荷兰ASML公司成立,专注于高端光刻机的研发和生产。1990年代,深紫外(DUV)光刻技术开始应用,使用波长为193nm的氟化氩(ArF)激光作为光源,分辨率进一步提高。

极紫外光刻技术的出现

进入21世纪,随着集成电路特征尺寸不断缩小,传统光刻技术面临极限。2001年,英特尔、IBM、AMD等公司联合成立极紫外(EUV)光刻联盟,推动EUV光刻技术的研发。2010年,ASML公司成功推出第一台商用EUV光刻机,使用波长为13.5nm的极紫外光作为光源,分辨率达到7nm以下,标志着光刻技术进入新纪元。

光刻技术的最新进展

近年来,光刻技术继续向更高分辨率、更高速度、更低缺陷率方向发展。多光束光刻、纳米压印光刻、电子束光刻等新技术不断涌现。2023年,ASML公司推出新一代EUV光刻机NXE:3800D,分辨率进一步提升,同时支持更薄的光刻胶和更小的工艺窗口。中国在光刻技术领域的投入也不断增加,多家企业和研究机构在EUV光刻、纳米光刻等方向取得重要进展。

半导体光刻技术的分类

按照曝光方式分类

接触式光刻

接触式光刻是最基本的光刻技术之一,它将掩模直接压在涂有光刻胶的晶圆上,通过紫外灯照射使光刻胶曝光。这种方法简单但容易导致掩模和晶圆损坏,且分辨率有限,主要用于研究和小批量生产。

接近式光刻

接近式光刻将掩模与晶圆保持一定距离,通过光学系统成像,提高了分辨率但仍然存在对准困难的问题。这种方法在20世纪70年代至80年代广泛应用于集成电路制造,随着技术进步逐渐被更先进的光刻技术所取代。

步进重复光刻

步进重复光刻是目前集成电路制造中最常用的光刻技术之一。它将掩模上的图案通过光学系统缩小并投射到晶圆上,每次曝光只曝光晶圆上的一个小区域,然后步进到下一个区域,重复这个过程直到整个晶圆曝光完成。这种方法具有高分辨率、高对准精度和高生产效率等优点,广泛应用于大规模集成电路制造。

扫描式光刻

扫描式光刻是一种先进的光刻技术,它通过扫描掩模和晶圆来实现大范围的曝光。具体来说,它将掩模和晶圆同时沿一个方向扫描,同时进行曝光,这样可以实现高分辨率和大曝光面积。扫描式光刻在大规模集成电路制造中具有重要应用,特别是对于需要高密度和高精度的芯片。

按照光源波长分类

可见光光刻

可见光光刻使用可见光作为光源,波长范围为400-700纳米。这种方法主要用于教学和研究,因为可见光的波长较长,分辨率有限,无法满足现代集成电路制造的需求。

紫外光光刻

紫外光光刻使用紫外光作为光源,波长范围为100-400纳米。这种方法的分辨率比可见光光刻高,可用于制造较精细的电路。紫外光光刻在20世纪70年代至80年代广泛应用于集成电路制造,随着技术进步逐渐被更先进的光刻技术所取代。

深紫外光刻

深紫外光刻使用深紫外光作为光源,波长范围为50-100纳米。这种方法的分辨率更高,可用于制造更精细的电路。深紫外光刻在20世纪90年代开始应用于集成电路制造,特别是对于0.25微米及以下的工艺。

极紫外光刻

极紫外光刻使用极紫外光作为光源,波长范围为10-50纳米。这种方法的分辨率极高,可用于制造极其精细的电路。极紫外光刻是目前最先进的光刻技术之一,广泛应用于7纳米及以下工艺的集成电路制造。ASML公司是极紫外光刻机的主要供应商,其NXE 系列光刻机是目前最先进的极紫外光刻机。

按照应用材料分类

硅基光刻

硅基光刻是目前集成电路制造中最常用的光刻技术,它在硅晶圆上进行光刻,用于制造各种半导体器件和集成电路。硅基光刻技术成熟,成本较低,适用于大规模生产。

有机材料光刻

有机材料光刻在有机材料上进行光刻,用于制造有机电子器件和柔性电子器件。有机材料光刻技术相对较新,仍在发展中,但具有灵活性好、成本低等优点,有望在未来得到更广泛的应用。

金属材料光刻

金属材料光刻在金属材料上进行光刻,用于制造微机电系统(MEMS)和微光学器件。金属材料光刻技术需要特殊的光刻胶和工艺,以适应金属材料的特性。

复合材料光刻

复合材料光刻在复合材料上进行光刻,用于制造多功能微结构和器件。复合材料光刻技术复杂,需要综合考虑各种材料的特性,是当前研究的热点之一。

按照工艺流程分类

干法光刻

干法光刻是通过光刻胶的曝光和显影来形成图案,然后通过干法刻蚀将图案转移到基材上。干法刻蚀通常使用等离子体或离子束,具有高选择性和高精度等优点,适用于深亚微米工艺。

湿法光刻

湿法光刻是通过光刻胶的曝光和显影来形成图案,然后通过湿法刻蚀将图案转移到基材上。湿法刻蚀使用化学试剂,操作简单,成本低,适用于简单的图案和大批量生产。湿法光刻在早期的集成电路制造中广泛使用,随着技术进步逐渐被干法光刻所取代。

无光刻胶光刻

无光刻胶光刻是一种新兴的光刻技术,它不需要使用光刻胶,而是通过直接刻蚀基材来形成图案。无光刻胶光刻技术包括电子束刻蚀、离子束刻蚀和聚焦离子束刻蚀等,具有高分辨率和高灵活性等优点,适用于研究和小批量生产。

3D光刻

3D光刻是一种能够在三维空间中形成微结构的光刻技术,包括立体光刻和数字光处理等。3D光刻技术适用于制造复杂的三维微结构和器件,如微流控芯片和微光学器件等。

按照应用领域分类

集成电路制造

集成电路制造是光刻技术最主要的应用领域,包括逻辑芯片、存储芯片和模拟芯片等的制造。光刻技术在集成电路制造中的应用最为广泛和成熟,技术迭代最快,对分辨率和精度要求最高。

微机电系统(MEMS)

微机电系统(MEMS)是将微电子技术和微机械技术相结合的系统,广泛应用于传感器、执行器和微泵等领域。光刻技术在MEMS制造中用于形成微结构和器件,包括表面微机械和体微机械等。

光电子器件

光电子器件是将光电子技术和微电子技术相结合的器件,包括激光器、光电探测器和光调制器等。光刻技术在光电子器件制造中用于形成微结构和器件,包括半导体激光器和光通信器件等。

生物医学器件

生物医学器件是用于生物医学领域的微器件,包括微流控芯片、生物传感器和药物输送系统等。光刻技术在生物医学器件制造中用于形成微结构和器件,具有高精度和高通量等优点。

半导体光刻技术的前沿技术

EUV光刻技术

极紫外(EUV)光刻技术是当前半导体制造领域的前沿技术之一。相比传统的深紫外光(DUV)光刻技术,EUV光刻使用13.5纳米波长的光源,这使得其在提高分辨率方面具有显著优势。

EUV光刻机的光源产生方式非常复杂,采用激光等离子体型光源,即利用高功率的激光击打金属锡,产生高温高密度的等离子体,辐射出极紫外光。这种技术虽然早在多年前就被证实,但直到最近才克服了技术难题,实现了商业化应用。

从2020年开始,台积电不再使用DUV技术,而是采用真正的13.5纳米波长的EUV锡激光技术来制造4纳米工艺的芯片。而2025年即将投入量产的2纳米芯片,其制造技术将更加依赖EUV光刻技术。

多光束光刻技术

多光束光刻技术是另一种前沿光刻技术,它使用多个电子束同时写入,可以显著提高光刻的吞吐量。与传统的单光束光刻相比,多光束光刻可以在更短的时间内完成相同的图案转移工作,这对于大规模生产具有重要意义。

多光束光刻技术的关键在于如何协调多个光束的工作,确保它们之间的同步性和一致性。这需要先进的控制系统和精密的机械结构来实现。虽然多光束光刻技术在分辨率方面可能不如EUV光刻,但在某些应用场景中具有优势,特别是在需要高通量的场合。

直写光刻技术

直写光刻技术是一种新兴的光刻技术,采用高速实时动态面扫描的直写技术。它利用大功率紫外激光或LED光源,通过高效集光系统和匀光系统,照射在数字微镜器件(DMD)上,通过数据链路实时动态地控制DMD的开闭状态,从而实现任意图形的直写。

直写光刻技术从传统曝光技术发展而来,其曝光成像原理与传统曝光技术类似,区别在于采用DMD取代传统的掩膜版或掩模。这种技术具有灵活性高、成本低、周期短等优点,特别适合于原型制作、小批量生产和研发阶段的测试。

芯碁微装主导起草的直写成像式曝光设备GB/T43725-2024《直写成像式曝光设备》国家标准已通过国家标委会的审核,将于2024年10月1日正式实施,这标志着直写光刻技术在标准化方面取得了重要进展。

纳米压印光刻技术

纳米压印光刻技术是另一种前沿光刻技术,它使用纳米尺度的模具,通过压印的方式在光刻胶上形成电路图案。这种方法具有高分辨率和低成本的优势,适用于大规模生产。

纳米压印光刻技术的关键在于模具的制作和压印过程的控制。模具的精度直接影响光刻的精度,而压印过程的控制则影响图案的完整性和一致性。这种技术在某些特定应用中已经显示出潜力,但还需要进一步研究和开发以提高其可靠性和适用性。

半导体光刻材料

光刻胶

光刻胶是光刻过程中最关键的材料之一,它是一种感光材料,由感光树脂、增感剂和溶剂三种主要成分组成的对光敏感的混合液体。根据全球半导体行业协会(SEMI)最新数据,光刻胶在半导体晶圆制造材料价值占比5%,光刻胶辅助材料占比7%,二者合计占半导体材料市场的相当比例。

光刻胶在大规模集成电路的制造过程中起着至关重要的作用,是图形转移介质,其利用光照反应后溶解度不同将掩膜版图形转移至衬底上。光刻胶主要由感光剂(光引发剂)、聚合剂(感光树脂)、溶剂与助剂构成。

光刻胶的生产工艺主要过程是将感光材料、树脂、溶剂等主要原料在恒温恒湿1000级的黄光区洁净房进行混合,在氮气气体保护下充分搅拌,使其充分混合形成均相。

根据曝光波长的不同,半导体光刻胶可分为多种类型:

紫外光刻胶:波长为300~450nm,包括G线光刻胶(436nm)和I线光刻胶(365nm),是市场上使用量最大的光刻胶。

深紫外光刻胶:波长为160~280nm,包括KrF光刻胶(248nm)和ArF光刻胶(193nm)。

极紫外光刻胶:波长为13.5nm,用于EUV光刻技术。

电子束光刻胶:用于电子束光刻技术。

离子束光刻胶:用于离子束光刻技术。

X射线光刻胶:用于X射线光刻技术。

光刻胶按极性可分为正光刻胶和负光刻胶。正光刻胶在曝光后会溶解,而负光刻胶在曝光后会硬化。

光刻胶的涂胶工艺目的是在晶圆表面建立薄的、均匀的、并且没有缺陷的光刻胶膜。一般来说,光刻胶膜厚从0.5μm到1.5μm不等,而且它的均匀性必须达到只有正负0.01μm的精度。

目前,全球半导体光刻胶供应市场高度集中,核心技术基本掌握在少数国际大厂手中。日本的JSR、东京应化、信越化学及富士胶片四家企业占据了全球70%以上的市场份额。我国光刻胶企业使用的树脂90%以上依赖进口,供应商以日本和美国厂商为主。全球光刻胶树脂主要由住友电木、日本曹达及美国陶氏等化工大厂供应。

国内光刻胶企业正在积极发展,如晶瑞股份、上海新阳、南大光电等。晶瑞股份是光刻胶及配套试剂的供应商,拥有百吨级环化橡胶系紫外负性光刻胶生产能力。

掩模材料

掩模(Photomask),又称光罩、光掩膜、光刻掩膜版等,是微电子、集成光电子制造中光刻工艺所使用的图形母版,由不透明的遮光薄膜在透明基板上形成掩膜图形,是承载图形设计和工艺技术等知识产权信息的载体。

掩模采用熔融石英(石英)板材料,通常为6英寸(~152毫米)见方,上面覆盖由不透明区域、透明区域和相移区域组成的图形。在光刻工艺中,图形被投射到晶圆上,从而形成一个集成电路的基本结构。

掩模的生产涉及CAM、光刻、检测三个主要环节,具体包括版图处理、图形转换、掩模制作和检测等步骤。掩模的加工技术主要有两种:其一为激光直写技术;其二为电子束直写技术。

全球第三方半导体掩模版市场主要被日本Toppan、美国Photronics、日本DNP三家公司控制。此前,全球具备掩膜基板精加工技术的企业主要有日本HOYA和韩国LG-IT两家企业,其余企业不具备掩膜和镀铬等加工能力,这使掩膜版生产厂商精加工后的基板主要依赖这两家企业供应。

显影剂

显影液(Developer)是溶解由曝光造成的光刻胶的可溶解区域的一种化学溶剂。光刻胶显影剂是半导体制造光刻工艺中的关键化学品,其作用是通过对曝光后的光刻胶进行显影,在半导体晶圆上形成所需的电路图形。

四甲基氢氧化铵(TMAH)是目前最常用的显影剂之一。2023年全球半导体TMAH显影液市场规模大约为449百万美元。显影剂的性能对光刻质量有重要影响,包括显影速度、选择比、分辨率和图案完整性等。

半导体光刻工艺

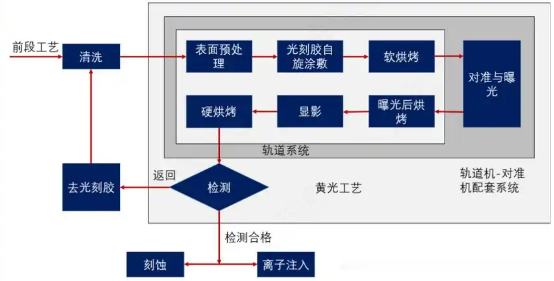

光刻工艺是半导体制造过程中最关键、最复杂的工艺步骤之一,耗时长、成本高。芯片制造可以包括多个工艺,如初步氧化、涂光刻胶、曝光、显影、刻蚀、离子注入等,这个过程需要用到的设备种类繁多。

完整的光刻工艺流程通常包括以下步骤:

1. 清洗硅片(WaferClean)

在光刻工艺开始前,需要对硅片进行清洗,以去除表面的污染物和杂质。清洗过程通常包括有机溶剂清洗、去离子水清洗和干燥等步骤,确保硅片表面干净、无缺陷。

2.预烘和底胶涂覆(Pre-bakeand Primer Vapor)

预烘是为了去除硅片表面的水分和挥发性物质,提高硅片的温度稳定性。底胶涂覆是在硅片表面涂覆一层底胶,以增强光刻胶与硅片表面的附着力,减少光刻胶的脱落和缺陷。

3.光刻胶涂覆(PhotoresistCoating)

光刻胶涂覆是将光刻胶均匀地涂覆在硅片表面。涂覆过程通常使用涂胶机(Coater)完成,通过高速旋转使光刻胶均匀展开。光刻胶膜的厚度和均匀性对后续工艺有重要影响,通常需要控制在严格的公差范围内。

4. 前烘(SoftBake)

前烘是为了去除光刻胶中的溶剂,提高光刻胶的稳定性。前烘温度通常低于后烘温度,以避免光刻胶过度硬化。

5. 对准(Alignment)

对准是将掩模与硅片对准的过程,确保图案能够准确地转移到硅片上。对准精度直接影响最终产品的质量和良率。现代光刻机通常使用自动对准系统,可以实现纳米级的对准精度。

6. 曝光(Exposure)

曝光是将光通过掩模投射到光刻胶上,使光刻胶发生化学反应。曝光过程中,光源的波长、曝光剂量和均匀性都会影响光刻质量。现代光刻机通常使用深紫外光或极紫外光作为光源,以实现更高的分辨率。

7. 后烘(PEB,Post-Exposure Bake)

后烘是在曝光后对硅片进行的热处理,目的是促进光刻胶的化学反应,提高图案的稳定性。后烘温度通常高于前烘温度,以确保光刻胶充分反应。

8. 显影(Develop)

显影是使用显影剂将曝光后的光刻胶图案显影出来。显影过程中,曝光区域的光刻胶被显影剂溶解,形成所需的图案。显影时间和显影剂的温度、浓度都会影响显影效果。

9. 硬烘(HardBake)

硬烘是为了进一步硬化光刻胶,提高其耐刻蚀性和热稳定性。硬烘温度通常高于后烘温度,以确保光刻胶能够承受后续的刻蚀工艺。

10. 刻蚀(Etch)

刻蚀是使用化学或物理方法将光刻胶图案转移到硅片上。刻蚀过程中,光刻胶作为掩蔽层,保护不需要刻蚀的区域。刻蚀工艺包括湿法刻蚀和干法刻蚀两种类型,具体选择取决于材料类型和工艺要求。

11. 去除(Strip)

去除是去除剩余的光刻胶,使硅片表面的图案清晰可见。去除过程通常使用有机溶剂或等离子体处理,确保完全去除光刻胶,不留任何残留物。

12.检验(Inspection)

检验是检查光刻质量的过程,包括检查图案的完整性、均匀性和缺陷等。检验过程通常使用CD-SEM、AFM等工具,确保光刻质量符合规格要求。

半导体光刻关键参数

光刻工艺的关键指标包括分辨率、灵敏度、套准精度、缺陷率等。以下是几个关键参数的详细说明:

分辨率(CriticalDimension, CD)

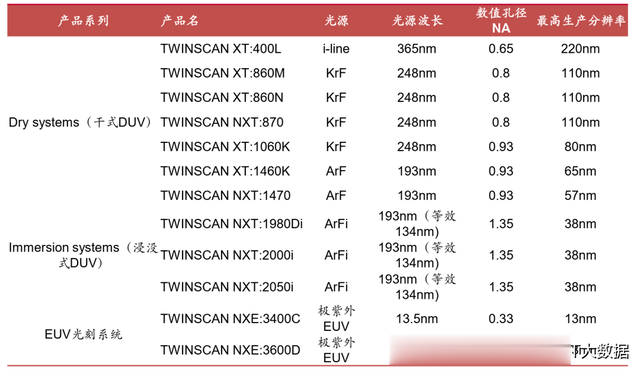

分辨率是指光刻工艺能够分辨的最小特征尺寸,通常用CD(CriticalDimension)表示。分辨率的大小直接影响集成电路的集成度和性能。根据当前主流的光刻机技术,i-line光刻机可实现350nm的分辨率,KrF光刻机可实现150nm分辨率,ArF光刻机可实现65nm分辨率,ArF浸没式光刻机可实现38nm分辨率。

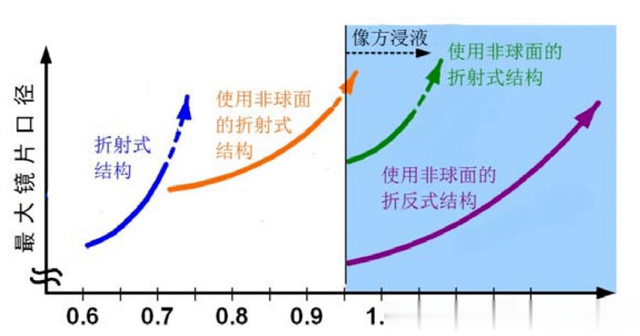

分辨率的计算公式通常为:CD= k1*λ/NA,其中k1是光刻胶的参数,通常在1~2之间;λ是曝光的波长;NA是数值孔径。

光刻工艺因子决定

光刻分辨率是光刻曝光系统最重要的技术指标,由光源波长、数值孔径、光刻工艺因子决定。根据瑞利准则,分辨率公式为R= k1 *λ/NA,λ代表光源波长,NA代表物镜的数值孔径,k1代表与光刻工艺因子。数值孔径指透镜与被检物体之间介质的折射率(n)和孔径角(2a)半数的正弦之乘积。公式为:NA=n*sinα 。n为投影物镜系统像方介质的折射率,α为投影物镜像方半孔径角。孔径角又称“镜口角”,是透镜光轴上的物体点与物镜前透镜的有效直径所形成的角度。孔径角越大,进入透镜的光通量就越大,它与透镜的有效直径成正比,与焦点的距离成反比。

瑞利准则指衍射极限系统中的分辨率极限。理想的成像系统,一个点所成的像是一个完美的点,但实际光学系统中的透镜具有一定的孔径大小,由此导致所成的像不是一个点,而是一个艾里斑。对于两个距离较近的点,所成的光斑也距离比较近。能够区分两个光斑的最小距离,就是分辨率。当一个艾里斑的中心与另一个艾里斑的第一极小值重合时,达到极限点,该极限被称为瑞利准则。

三方面提高光刻机分辨率:增大数值孔径、缩短波长、减小光刻工艺因子。分辨率指投影光学系统在晶圆上可实现的最小线宽。光刻机分辨率由光源波长、数值孔径、光刻工艺因子决定。因此可以从以下三方面提高分辨率:1)增大投影光刻物镜的数值孔径;2)缩短曝光波长;3)减小光刻工艺因子。

1)增大投影光刻物镜的数值孔径:一方面可以改进投影式透镜系统来增大入射角,另一方面可以采用折射率高的介质-浸润式。非球面的使用能够在不增加独立像差数的前提下,增加自变量的个数,有利于改善像质,同时在同等约束条件下,减少了光学元件的数量。非球面的应用使物镜NA可以增加到0.9,接近物理极限(干式光刻);引入浸没式技术后,物镜NA可以增加到1.1以上(浸没式光刻);加入反射镜组成折反式结构理论上物镜NA可到1.35 (极限值)。趋势为(干式)球面镜→非球面镜→(浸没式)非球面镜→折返式。

2)缩短曝光波长:由于晶体管越做越小,元件线路越来越密集,光刻机需要达到更高的分辨率,因此必须要寻找波长越来越短的光源。

3)减小光刻工艺因子:计算光刻OPC——在掩膜上增加辅助结构来消除图像失真,实现分辨率的提高;离轴照明OAI——通过采用特殊光源让正入射方式光变成斜入射方式,目的是在同等数值孔径内容纳更多的高阶光,从而曝光更小尺寸结构,提高分辨率;相移掩膜PSM——当两个光源进行成像时会在重合部分产生干涉效应,使光强增大,导致两个光源不能有效地区分开,如果通过改变掩膜结构在其中一个光源处采用180度相移,这两处光源产生的光会产生相位相消,光强相消,两个光源可以区分开,提高分辨率。

工艺因子已突破理论极限:理论上对于单次曝光k1 的最小极限约为0.25,通过组合使用OPC、多重图形等分辨率增强技术,光刻工艺因子已突破其理论极限0.25。

套准精度(Overlay)

套准精度是指相邻层之间的对准精度,通常以套准误差(OverlayError)表示。套准精度直接影响集成电路的良率和性能。现代光刻技术的套准精度可以达到纳米级别,以满足先进工艺节点的要求。

线宽均匀性(LineWidth Variation, LWV)

线宽均匀性是指光刻图案的线宽在不同位置的一致性。线宽均匀性的好坏直接影响电路的性能和可靠性。通常使用线宽变化率来衡量线宽均匀性,变化率越小,均匀性越好。

覆盖率(Coverage)

覆盖率是指光刻胶在硅片上的均匀涂布程度。覆盖率的高低直接影响光刻胶膜的厚度和均匀性,进而影响光刻质量。通常需要控制光刻胶膜的厚度在严格的公差范围内,以确保光刻图案的准确性和一致性。

趋肤效应(SkinEffect)

趋肤效应是指光刻胶在曝光时的体积收缩现象。趋肤效应会导致图案的高度不均匀,影响刻蚀后的图案质量。通过优化光刻胶配方和工艺参数,可以减小趋肤效应的影响。

显影速率(DevelopmentRate)

显影速率是指显影过程中光刻胶的去除速率。显影速率的快慢直接影响显影时间和显影质量。通常需要控制显影速率在适当的范围内,以确保显影均匀、无缺陷。

半导体光刻质检标准

检测方法

光刻工艺后的检查:确保图形正确形成,无显影缺陷和颗粒污染。主要的检测方法包括:

CD-SEM测量:CD-SEM(Critical Dimension Scanning Electron Microscope)是测量临界尺寸的常用工具。它通过扫描电子显微镜观察和测量光刻图案的尺寸,可以精确测量线宽、间距等参数。中国科大主导制定的半导体线宽检测国际标准(ISO)文档指定了利用CD-SEM成像表征刻蚀线宽的结构模型及其相关参数、Monte Carlo模拟模型和成像扫描线计算方法、MBL数据库构造方法和文件。

AFM测量:AFM(Atomic Force Microscope)原子力显微镜可以测量光刻图案的表面形貌和三维结构,适用于纳米级图案的检测。

电子显微镜检查:电子显微镜可以观察光刻图案的细节,检测缺陷和异常。

叠加测量:叠加测量工具用于测量相邻层之间的套准精度,确保图案对准准确。

质检标准

半导体光刻的质检标准由各种标准化组织如ISO和国家机构如全国半导体设备和材料标准化技术委员会制定。主要的质检标准包括:

尺寸精度:光刻图案的尺寸必须符合设计规格,通常以CD误差表示。

套准精度:相邻层之间的套准误差必须小于允许值,通常在纳米级别。

缺陷率:光刻图案中的缺陷数量必须低于允许值,包括颗粒污染、断线、短路等缺陷。

均匀性:光刻图案在硅片上的均匀性必须符合要求,包括线宽均匀性、覆盖率等。

耐刻蚀性:光刻胶的耐刻蚀性必须足够,以承受后续的刻蚀工艺。

芯碁微装主导起草的直写成像式曝光设备GB/T43725-2024《直写成像式曝光设备》国家标准已通过国家标委会的审核,将于2024年10月1日正式实施,这为直写光刻技术提供了重要的质检标准。

半导体光刻工装治具

涂胶机

涂胶机是用于在硅片上涂覆光刻胶的设备。涂胶机通过高速旋转使光刻胶均匀展开,形成薄的、均匀的光刻胶膜。涂胶机的关键参数包括转速、温度、时间等,这些参数会影响光刻胶膜的厚度和均匀性。

光刻机

光刻机是芯片制造中最复杂、最昂贵的设备。光刻机用于将掩模上的图案转移到光刻胶上,是光刻工艺的核心设备。光刻机的关键参数包括分辨率、套准精度、产能等[55]。

ASML是全球领先的光刻机制造商,于1984年成立,40年来公司产品布局专注于IC前道光刻机,从创业之初的筚路蓝缕,几经突破后终成光刻巨人。2023年,ASML实现营收276亿欧元(约2150亿人民币)。

光刻机采用的方法是激光等离子体型光源,即利用高功率的激光击打金属锡,产生高温高密度的等离子体,辐射出极紫外光。这种方法很久之前就被证实,但是起初面临诸多技术挑战。

显影机

显影机是用于显影光刻胶的设备。显影机通过控制显影剂的温度、浓度和流量,确保显影过程均匀、无缺陷。显影机的关键参数包括显影时间、显影温度、显影剂流量等。

刻蚀机

刻蚀机是用于将光刻胶图案转移到硅片上的设备。刻蚀机包括湿法刻蚀机和干法刻蚀机两种类型。湿法刻蚀机使用化学溶液进行刻蚀,干法刻蚀机使用等离子体或离子束进行刻蚀。刻蚀机的关键参数包括刻蚀速率、选择比、均匀性等。

中微半导体于2018年成功研制7nm的刻蚀机,这是国产造芯的一大进步。然而,成功研制刻蚀机并不代表我们就有能够制造7nm制程的芯片的实力,因为还需要其他设备和工艺的支持。

清洗机

清洗机是用于清洗硅片的设备。清洗机通过有机溶剂、去离子水等介质,去除硅片表面的污染物和杂质。清洗机的关键参数包括清洗温度、清洗时间、干燥方式等。

烘烤炉

烘烤炉是用于对硅片进行热处理的设备。烘烤炉用于前烘、后烘、硬烘等工艺步骤,通过控制温度和时间,实现不同的工艺目标。烘烤炉的关键参数包括温度控制精度、温度均匀性、升温速率等。

半导体光刻设备供应商

光刻机供应商

光刻机是半导体设备中最昂贵、最关键、国产化率最低的环节,全球光刻机市场被荷兰ASML、日本佳能、尼康三大巨头垄断。

ASML(AdvancedSemiconductor MaterialsLithography)于1984年成立,40年来公司产品布局专注于IC前道光刻机,从创业之初的筚路蓝缕,几经突破后终成光刻巨人。2023年,ASML实现营收276亿欧元(约2150亿人民币)。目前,ASML供应商大多都主要来自欧美及亚洲国家,比如EUV光刻机大约有5000个供应商,其中来自荷兰本土的供应商大约是1600个,占比32%左右;来自北美和亚洲的供应商都是1350个,各占27%左右。

佳能(Canon)和尼康(Nikon)是另外两家主要的光刻机供应商。尼康作为全球为数不多可以生产光刻机的制造商,将继续运用其享誉世界的"光利用技术"和"精密技术",为客户提供解决方案。

上海微电(SMEE)是国内主要的光刻机供应商之一,成立于2002年,致力于半导体装备研发和生产。当前全球半导体光刻机厂商主要包括ASML、Nikon、Canon,其中ASML占据全球8成以上市场,垄断高端EUV领域。

光刻胶供应商

全球半导体光刻胶供应市场高度集中,核心技术基本掌握在少数国际大厂手中。日本的JSR、东京应化、信越化学及富士胶片四家企业占据了全球70%以上的市场份额。

JSR(日本合成橡胶)、东京应化(TOK)、信越化学和住友化学等公司不仅是该领域的核心供应商,在高端半导体光刻胶市场上,日本企业更是占据着约80%的市场份额。

我国光刻胶企业使用的树脂90%以上依赖进口,供应商以日本和美国厂商为主。全球光刻胶树脂主要由住友电木、日本曹达及美国陶氏等化工大厂供应。

国内光刻胶企业正在积极发展,如晶瑞股份、上海新阳、南大光电等。晶瑞股份是光刻胶及配套试剂的供应商,拥有百吨级环化橡胶系紫外负性光刻胶生产能力。

掩模供应商

全球第三方半导体掩模版市场主要被日本Toppan、美国Photronics、日本DNP三家公司控制。此前,全球具备掩膜基板精加工技术的企业主要有日本HOYA和韩国LG-IT两家企业,其余企业不具备掩膜和镀铬等加工能力,这使掩膜版生产厂商精加工后的基板主要依赖这两家企业供应。

Photronics是一家美国的光掩模制造商,提供高质量的光掩模和掩模解决方案。他们的制造工厂遍布全球,为还原性分划板(主要是2X至5X)、Ultratech1X分划板和标准1X光掩模——以及一系列的掩模尺寸从4英寸到14英寸的集成电路制造提供本地解决方案。

SUSSMicroTec是一家总部位于德国的半导体设备供应商,专注于微结构设备和工艺解决方案。Compugraphics是一家英国的光罩制造商,提供高质量的光罩和掩模解决方案。

其他材料供应商

光刻胶显影剂供应商:四甲基氢氧化铵(TMAH)是目前最常用的显影剂之一。2023年全球半导体TMAH显影液市场规模大约为449百万美元。

光刻胶树脂供应商:全球光刻胶树脂主要由住友电木、日本曹达及美国陶氏等化工大厂供应。

掩模基板供应商:日本HOYA和韩国LG-IT是全球主要的掩模基板供应商。

结论与展望

半导体光刻技术是集成电路制造的核心技术,经历了从简单到复杂、从粗糙到精密的漫长发展过程。从最初的可见光到现代的极紫外光,从微米级到纳米级,光刻技术不断突破极限,推动着微电子技术以前所未有的速度发展。

当前,EUV光刻技术已经成为先进工艺节点的主流技术,而多光束光刻、直写光刻、纳米压印等新兴技术也为未来提供了多种可能。然而,光刻技术的发展仍然面临诸多挑战,包括光源、光刻胶、掩模等关键材料的开发,以及分辨率、套准精度、缺陷率等关键参数的进一步优化。

对于新兴国家来说,发展半导体光刻技术需要从人才培养、技术引进、自主创新等多个方面入手,建立完整的产业链和生态系统。同时,也需要加强国际合作,共同推动光刻技术的发展。

未来,随着新材料、新工艺、新设备的不断涌现,光刻技术将继续突破物理极限,为集成电路技术的持续进步提供坚实基础。新兴国家应抓住这一历史机遇,加强半导体光刻技术的研发和应用,提升自身的半导体产业竞争力。

半导体厂务