当我们的手机处理器与内存以每秒数GB的速度交换数据,或是路由器千兆端口传输高清视频流时,信号完整性就是背后的无名英雄。其中,反射系数(Γ)作为衡量信号完整性的核心指标,直接决定了数据能否准确、高效地穿越电路板。本文将从实战角度解析反射系数的计算、成因与抑制策略,助力突破高速设计瓶颈。

正如SI大神Eric Bogatin所说:有两种工程师,一种是已经遇到了信号完整性问题,另一种是即将遇到信号完整性问题。

一、 反射系数是信号完整性的核心度量

在高速信号传输中,信号遇到阻抗不连续点时(如连接器、过孔、分支走线,阻抗突变等),部分能量无法继续向前传输,而是像回声一样“反弹”回源端,这就是信号反射。反射系数(Γ)量化了这一反弹能量的比例:Γ = (ZL - ZS) / (ZL + ZS)

其中:ZL即负载阻抗(如接收端芯片输入阻抗、传输线末端阻抗)

ZS即源阻抗(如驱动芯片输出阻抗、传输线特性阻抗)

这里有两个最核心结论,第一当 ZL = ZS 时,Γ = 0,实现完美匹配(理想状态,无反射)。

第二当 ZL 与 ZS 差异越大,|Γ|越接近1,反射越严重(|Γ|=1表示全反射)。

小知识:为什么50Ω如此普遍?在消费电子领域中常见50Ω单端阻抗(如HDMI, DDR时钟线)或90/100Ω差分阻抗(如USB, MIPI, PCIe)。这是源阻抗、传输线功率传输能力及损耗特性之间的最为合适的工程平衡点,已成为行业默认标准。偏离此标准将显著增加反射风险,是PCB layout设计需要重点关注的。

二、 反射系数计算实战与典型场景分析

案例1某HDMI接口阻抗失配某终端HDMI输出端设计目标阻抗为100Ω差分。由于PCB叠层计算误差和加工波动,实测走线阻抗仅80Ω。接收端芯片输入阻抗典型值要求为100Ω。

反射系数计算为Γ = (Z_L - Z_S) / (Z_L + Z_S) = (100 - 80) / (100 + 80) = 15 / 185 ≈ 0.111

反射电压幅度 = Γ * 入射电压 ≈ 0.111 * 信号幅度。在480MHz的TMDS时钟信号上,此反射与后续信号叠加,导致眼图闭合(估算眼高下降明显),从而引发视频输出间歇性闪烁。解决方案:优化走线参数(加宽线距、调整介厚),确保阻抗控制在95Ω-105Ω范围。

案例2某WiFi 6路由器DDR4内存过孔阻抗突变某路由器采用DDR4-3200内存,主控与DRAM间需穿越多个信号层。过孔残桩(Stub)过长导致局部阻抗下降至约40Ω(目标50Ω)。

反射系数计算(过孔处):Γ = (50 - 40) / (50 + 40) = 10 / 90 ≈ 0.111

在1.6GHz的高频下(DDR4-3200数据率),该反射点与其它不连续点产生的多次反射叠加,导致数据窗口抖动增大(实测增加约35ps)。最终通过使用背钻(Backdrill)技术去除多余残桩,将阻抗提升至48Ω,抖动显著改善。

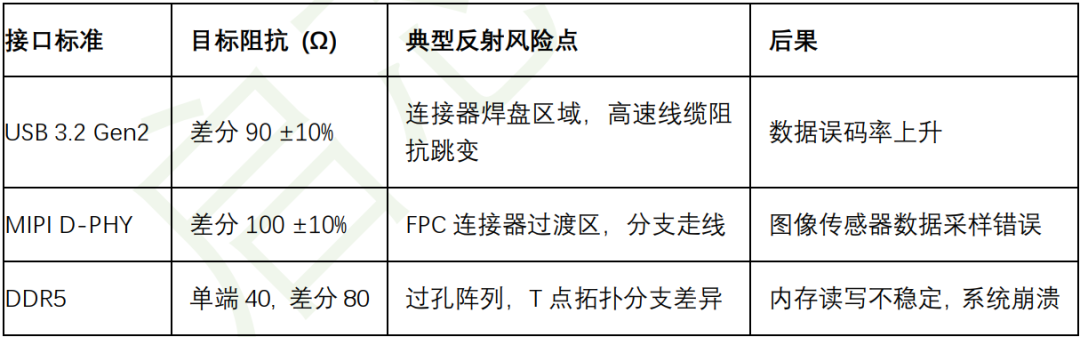

表:常见接口特性阻抗与典型反射风险点

三、 反射抑制核心对策

首先是源头控制最重要,精准阻抗设计与制造。可以仿真先行,利用SI工具(如ADS, HyperLynx)在布局前仿真走线阻抗, 优化线宽/间距/叠层。手机SoC与LPDDR5间布线常需多次迭代,最终定稿。同时工艺严格管控,明确要求PCB厂控制阻抗公差(通常±10%)。高速接口(如PCIe 5.0)要求±7%甚至更严。提供足够多的阻抗测试条(Coupon)是很有必要的。还有处理好参考平面,要确保高速线下有完整、无分割的参考平面(GND或电源)。避免跨分割, 防止阻抗突变和额外串扰。

然后匹配策略是消耗反射能量。其中端接电阻(Termination)被公认为最常用且有效的方案。比如源端串联匹配,即在驱动器输出端串联电阻(Rs ≈ Z0 - Z_driver_output)。适用于点对点时钟信号(如手机主控到内存的CLK线)。其优势是功耗低、布线简单。

以及还有这三种也非常常用。

1.末端并联匹配,在接收器输入端并联电阻到地或电源(Rt = Z0)。常用于较低速总线或拓扑末端。缺点是直流功耗增加。

2.戴维南(Thevenin)端接,方法是双电阻分压网络, 提供上拉和下拉。能同时匹配阻抗和优化电平, 但功耗较大, 多用于关键差分对(如USB HSIC)。

3.拓扑优化策略是对于多负载(如多个DDR颗粒), 优先选用Fly-by拓扑(菊花链)而非T型分支, 减少阻抗不连续点。严格控制分支长度(Stub length << 信号上升沿空间长度)。

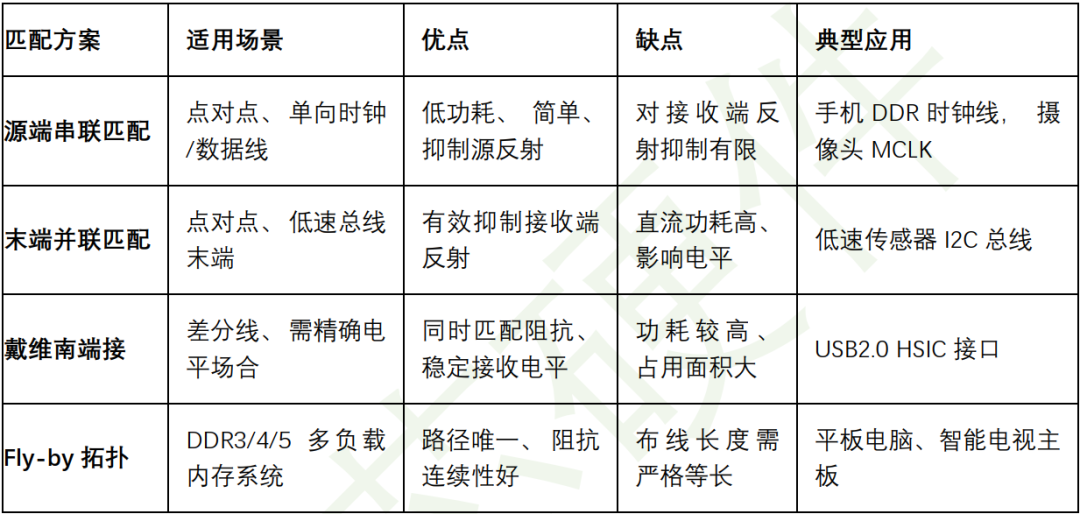

表:不同匹配方案效果对比

最后是结构优化实现最小化不连续性,主要用到以下的核心技术,比如过孔youhua 设计,通过使用小孔径(如8/16mil)、 移除无用焊盘(NPTH)、 采用背钻(Backdrill)消除长残桩。射频及超高速数字电路(如毫米波, PCIe 6.0)常用激光孔。这些我在前面文章都有详细介绍,为什么能实现优化。其次是连接器与焊盘选择特性阻抗匹配的连接器。优化BGA焊盘平静瓶颈区域走线, 避免突然加宽或缩窄。使用渐变线(Taper)过渡。最后是层间过渡,要特别避免高速信号线在参考平面切换层时跨越大分割区域。必要时增加缝合电容(Stitching Capacitor)提供高频回流路径。

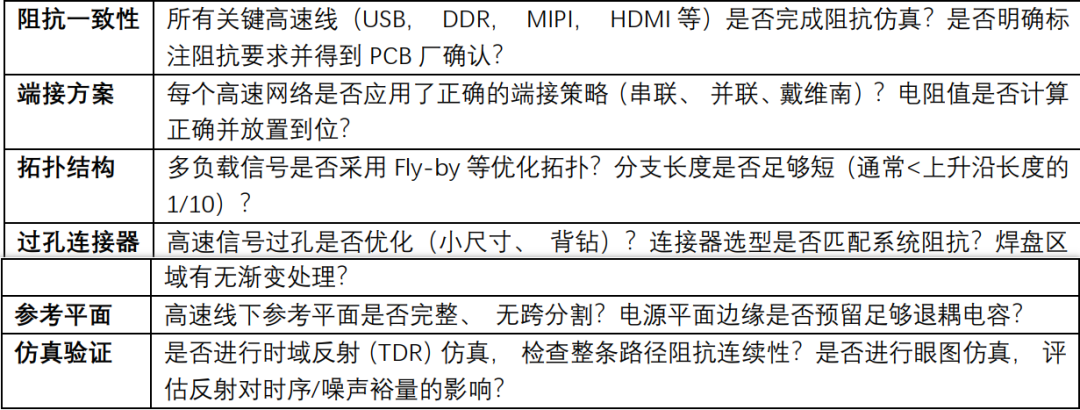

四、 细化设计检查表

在完成设计前,重点使用此检查表快速评估反射风险可以事半功倍,我每次设计完都会核对一下,然后不断更新,加入新的检查项目,让我的设计失误率有了很大的降低。

总结

在电子产品日益追求小型化、 高频化与低功耗的今天, 反射控制能力已成为硬件工程师的核心竞争力。从精准的阻抗计算与仿真, 到合理的端接策略与结构优化, 每一步都是工程智慧与严谨态度的结合。

优秀的硬件设计如同交响乐, 反射控制确保了每个信号音符的纯净与准时。当你的设计成功跨越GHz门槛, 实现稳定流畅的数据洪流时, 那些隐藏在PCB层间的阻抗匹配细节, 正是工程师专业精神的最佳注脚。在高速世界里, 忽视反射等于容忍失真。