硅基异构集成和三维集成可满足电子系统小型化高密度集成、多功能高性能集成、小体积低成本集成的需求,有望成为下一代集成电路的使能技术,是集成电路领域当前和今后新的研究热点。硅基三维集成微系统可集成化合物半导体、CMOS、MEMS等芯片,充分发挥不同材料、器件和结构的优势,可实现传统组件电路的芯片化、不同节点逻辑集成电路芯片的集成化,从而提升信号处理等电子产品的性价比。梳理了晶圆键合装备的工艺过程、主要厂商及市场需求、我国晶圆键合设备研发现状,并展望了晶圆键合设备的技术发展趋势。

0 引言

半导体与集成电路产业是面向世界科技前沿、面向经济主战场、面向国家重大需求的重要产业,也是近期国际经济与科技竞争的焦点。2018年,中国成为全球半导体第一大市场,2019年,全球半导体市场销售额达4 183亿美元。集成电路产业是半导体产业中最大的消费领域,多年来销售占比重达80%以上,行业销售收入年均增速超过20%[1]。

在摩尔定律的引导下,集成电路(Integrated circuit,IC)行业一直高速发展,晶体管特征尺寸己经从90 nm向7 nm迈进[2]。然而,由于随着晶体管特征尺寸已日益接近物理极限,量子效应和短沟道效应越来越严重[3-4],内部电子自发地通过源极和漏极,导致漏电流增加,进而限制了晶体管的进一步缩小。因此,按照摩尔定律的方式,通过缩小晶体管特征尺寸来提升集成电路性能、降低功耗变得越发困难。晶体管将会快速地接近约5 nm的极限栅极长度,因此探索新的沟道材料和器件结构是推动IC产业继续发展的两条极为重要的路线[5-7]。

三维(Three-dimensional,3D)集成是超越摩尔一个至关重要的研究应用方向[8-9]。3D集成的定义是将摩尔晶圆或芯片在垂直于晶圆或芯片平面方向上进行堆叠[10]。集成电路技术由二维平面向三维方向发展,该技术分段实现,首先实现几层的三维集成,随着时间的推移,三维集成芯片层数将会不断增加。采用全新结构的3D集成是推动半导体行业发展的重要技术,诸如存储器、逻辑器件、传感器和处理器等不同类型的器件和软件的复杂集成,以及新材料和先进的芯片堆叠技术,都要基于3D集成技术[11]。3D集成技术存在着4项挑战,分别为晶圆级对准精度、键合完整性、晶圆减薄与均匀性控制以及层内(层间)互联[12]。

随着摩尔定律逼近材料与器件的物理极限,源于微机电系统(Micro Electro Mechanical Systems,MEMS)制造技术的晶圆级封装键合技术逐渐进入集成电路制造领域,成为实现存储器、逻辑器件、射频器件等部件的三维堆叠同质/异质集成,进而提升器件性能和功能,降低系统功耗、尺寸与制造成本的重要技术途径,对满足集成电路高集密度、高功能密度和高性能集成的迫切需求,突破国内自主可控平面集成能力不足的瓶颈,实现集成电路由平面集成向三维立体集成的跨越式发展有重要的战略价值[13]。因此,英特尔、三星、华为、高通、罗姆、台积电等知名企业及众多高校、科研院所均围绕晶圆级封装键合开展了设备、器件、工艺的研究。

1 晶圆键合设备及工艺过程

晶圆键合设备通过化学和物理作用将两块同质或异质晶片紧密地结合起来,从而实现微电子材料、光电材料及其纳米等级微机电元件的电气互联、功能集成和器件封装。晶圆键合设备广泛应用于射频器件、惯性器件、光电器件、信息处理器件及3D集成逻辑集成电路的先进封装制造,对位精度、键合温度均匀性、键合压力范围及控制精度对晶圆键合工艺具有重要影响。

如图1所示,晶圆键合工艺过程为:首先将待键合的一组晶圆进行预处理、清洗、视觉对准,进而通过不同方法实现晶圆对的键合。晶片接合后,界面的原子受到外力的作用而产生反应形成共价键结合成一体,并使接合界面达到特定的键合强度,称之为永久性键合。若借助粘结剂将晶片接合,也可作为临时键合,通过将器件晶圆固定在承载晶圆上,可为超薄器件晶圆提供足够的机械支撑,保证器件晶圆能够顺利安全地完成后续工艺制程,如光刻、刻蚀、钝化、溅射、电镀和回流焊。

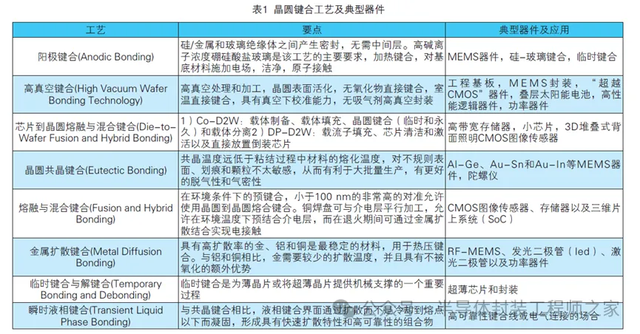

具体的晶圆键合工艺可按照键合材料、键合手段、应用场景分类,方法不尽相同,按照键合工艺对晶圆键合分类(见表1)。

晶圆级键合是半导体器件物理、材料物理化学、精密机械设计、高精度自动控制等多学科交叉的科学技术领域。晶圆键合工艺中晶圆尺寸的扩大、芯片特征尺寸的缩小、异质材料之间的热失配及晶格失配等重要技术问题还有待解决[14]。国外利用超高真空Ar快速原子束表面活化键合工艺实现了大面积、高强度的晶圆级键合,但我国在大面积、高强度晶圆级键合理论与工艺领域能力仍有待提高。晶圆键合及烘烤激活对晶圆表面温度均匀性及翘曲变形有十分严格的要求。温度均匀性取决于设备结构、加热工艺以及晶圆自身的热物理性能,翘曲变形则受温度均匀性、外加机械力以及晶圆自身力学性能的影响。传统的研究多采用实验试错的方法,没有将上述因素协同考虑,难以获得优化的结构工艺参数,导致键合可靠性及器件良率大大下降。国际上的高水平研究团队通常结合先进的数值仿真手段及多变量多目标优化方法,综合考虑包含热辐射、热传导在内的热场以及包含热应力、机械应力在内的应力场等多物理场之间的复杂耦合作用机理,开展对晶圆键合和烘烤激活工艺参数的协同优化,从而大大提高键合品质及器件良率。

2 晶圆键合设备主要厂商

随着先进封装趋势向着更复杂的异质集成、更大的封装载体、更薄的芯片以及更小的封装尺寸等方向发展,发达国家晶圆键合设备市场已比较成熟,而我国市场仍处成长阶段,未来将成为全球晶圆对准设备消费增长的主要推动力。在企业不断加大资金投入、基础研究深度拓展和消费者认知不断提高的基础上,晶圆键合系列设备市场将迎来井喷式发展。目前,国际一流晶圆键合设备厂商主要包括奥地利EVG公司与德国SUSS MicroTec公司等,详见表2。

奥地利EVG公司的主流产品,适合阳极键合、共晶键合、金属扩散键合、直接键合、聚合物键合、熔融与混合键合和瞬时液相键合的小批量、半自动晶圆键合解决方案,如EVG510、EVG520、E V G 5 4 0 晶圆键合系统;也可以提供全自动、大批量、满足3D异构集成高对准精度生产的晶圆键合解决方案,如EVG560、EVG GEMINI、EVG Combond、EVG Bondscale等晶圆键合系统;还有用于扇出封装、晶圆减薄、3D堆叠、晶圆键合的临时键合和晶圆解键合解决方案,如EV G 8 5 0 、EVG850TB、EVG850LT等晶圆临时键合与解键合系统;晶圆对准设备由Smartview发展到Smartview3,对准精度提高到50 nm。

晶圆键合设备总体技术发展方向是高精度、高集成化、高可靠性、高动态、高效化的趋势,关键技术指标为:对准精度≤50 nm;键合温度均匀性≤±1%;最大晶圆尺寸304.8 mm(12英寸);最大键合压力100 kN;最高键合温度550 ℃。

德国SUSS MicroTec拥有六十多年的历史,是半导体行业领先的微结构工艺设备制造商,产品涵盖光刻、涂胶/显影、晶圆键合、光刻掩膜版清洗等诸多半导体、微加工相关领域。SUSS晶圆键合系统主要包括XB8、SB6/8Gen2、XBS200、XBS300、XBC300 Gen2等系统,最大晶圆尺寸304.8 mm(12英寸),对准精度≤500 nm,能够满足包括共晶、直接键合等各种晶圆键合工艺需求。

国内设备起步晚,国内键合设备技术发展方向由手动向半自动转换,国内没有多模块集成的晶圆键合设备,与国外设备代差距较大。上海微电子装备(SMEE)有独立对准、键合、解键合等设备,SWB系列晶圆键合设备用于有机胶键合、玻璃浆料键合、共晶键合、阳极键合等工艺。SWA系列晶圆对准设备对准精度≤±2 μm。苏州美图开发的阳极晶圆键合设备,最大键合压力10~30 kN,最高温度450 ℃。中国电科2所研制真空晶圆键合系统对准精度≤1 μm,键合温度均匀性≤±1%(FS),设备达到国内先进水平(如图2所示)。

3 我国晶圆键合设备的研发现状

晶圆键合设备是进入壁垒很高的产业,对于光学系统、图像处理与识别、高精度晶圆平行移动等技术的要求极高。国内的众多设备厂家因自身的人才、技术、设备、材料和资金等各方面因素的制约,无力进行设备持续的研究和改进,与国外同行之间的技术和实力的差距有扩大的趋势,晶圆键合产品在技术性能、质量可靠性、稳定性等方面存在很大的不足。目前,国内晶圆级键合技术主要受限于国内器件设计与工艺、设备稳定性与精确度等领域的基础理论与关键技术的发展水平。

3.1 技术性能

目前国内生产的最好的设备对准精度为±2 μm,与国外设备差距较大,EVG对准精度≤50 nm。键合温度均匀性规格书≤±1%(FS),实际能达到≤±0.6%。

目前在晶圆级封装行业内,临时键合技术的使用已经比较成熟,但都是厚度都在100 μm以上的单层硅通孔(TSV)结构,受限于临时键合材料,暂不能做到更薄。临时键合稳定的另一面是解键合和清除残胶更加麻烦,需要更长时间去除残胶,键合的稳定和解键合残胶的易清洁之间的平衡,还需要更长时间去解决。

国外设备自动化程度可满足大生产线需求,国内设备差距很大。

3.2 质量可靠性

国外设备键合热台使用寿命长、密封可靠性高,加压气液缸、检测传感器、卡盘等关键件可靠、耐用,设备一致性、长期使用稳定性好,加热台互换性良好。国内设备、键合加热台等部件一致性差,稳定性不好,缺乏关键零部件持续攻关及工艺深度结合。

3.3 研发模式及投入

我国设备行业与国外行业领军企业的研发模式有很大不同。以半导体装备龙头企业AMSL为例,在全球范围内与优势单位、头部企业合作,实现优势互补、强强联合,分布在全球的700多家供应商提供的功能模块和单元组件贡献了AMSL光刻设备约85%的外购成本。AMSL能专注于自身独特的能力优势,集成世界范围内最专业的制造商来设计、研发与制造光刻机,与比利时的IMEC光刻研究中心保持着长期合作关系,依靠强大的研发实力引领市场、开拓创新,拥有庞大且涉及多学科多领域的高科技研发团队,每年用于研发的费用数以亿计。自2015年以来,AMSL的研发人数占员工总数的比例一直维持在35%左右,研发人员逐年递增,2018年达8 500多人[15]。国内装备研制企业与零部件生产商配合不紧密,产学研合作脱节,研究方向不专注,高端人才缺乏,研发投入不够,缺乏长期战略投入,造成与国外高端核心装备的技术差距较大。

4 晶圆键合设备技术发展趋势

4.1 向全自动多工艺集成方向转换

设备由单一工艺段设备逐步全自动多工艺集成方向转换,表现出高集成度特点。近年来半自动晶圆键合设备市场份额在逐渐下降,全自动晶圆键合设备市场份额逐年在提高。集束型晶圆键合设备由若干功能不同的工艺腔构成,会产生大量与工艺相关的数据,每个工艺腔内布置大量检测不同物理量的传感器,在设备运行期间还会产生大量数据。通过使用合适的数据处理方案处理上述海量数据,可有效地反馈至各部分设计人员,从而辅助设备设计以及器件控制方案。对集成型先进封装键合设备而言,生产过程较复杂,而腔室之间处理晶圆的片数、时间也不相同,导致腔内机械手时域作业调度方案优劣在很大程度上会影响集束型设备生产效率以及设备运作流畅性,因此科学地设计集束型设备生产过程模型以及机械手调度算法对生产效率至关重要[16]。此外,国际IC装备和材料协会(SEMI)针对集束型装备控制软件(CTC)的控制软件正向标准化、通用化控制系统发展,符合国际标准CTC的控制软件是国际上IC装备控制系统的通用解决方案。因此,为使晶圆键合设备可以进入标准化生产线,需要针对SEMI标准设计CTC软件。

4.2 向3D集成技术领域转化

设备由MEMS领域应用转化到3D集成技术领域,表现出高对准精度特点。大多数对准、键合工艺都源于微机电系统(MEMS)制造技术,但应用于3D集成的对准精度要比传统MEMS对准精度提高5~10倍,目前设备对准精度已经达到亚微米级。实现晶圆级对准的方法有顶部对准或者底部对准(TSA/BSA)、红外透射对准(IR)、片中间对准(ISA)/面-面对准、背对背对准(如图3所示)。顶部对准或者底部对准采用一组物镜,这种方法要求一片晶圆是透明的或具有一定的透光性,从上侧或者下侧都可以看到上下两个晶圆的标识(Mark)点。红外透射对准技术广泛应用于3D IC晶圆级键合领域,能够实施对Mark进行测量实时成像,多次对准,进一步提高对准精度。红外透射对准的优点是可实时成像,多次对准;缺点是对准精度与晶圆的厚度相关,波长选择与材质和厚度相关,并且随着厚度增加,成像质量下降,叠层晶圆出射面的粗糙度与红外透射对准精度也相关。背对背对准需要双面光刻,或者背面光刻。

当上述方式都不满足对准要求时,可以采用片中间对准(ISA),这种对准方式的主要缺点是需要对准的晶圆Z 方向的间距大。EV Group采用SmartView对准系统。

设备由MEMS领域应用转化到3D集成技术领域,表现大压力高温度均匀性特点。键合台由金属加热器向陶瓷加热器转化,进一步提高温度均匀性及耐磨性。晶圆尺寸由203.2 mm(8英寸)转向304.8 mm(12英寸),低温直接键合增多,键合压力增大至100 kN。

总之,晶圆键合设备在后摩尔时代表现出来高集成、高精度、大压力高温度均匀性、高动态和智能化的特点,晶圆键合设备在3D集成技术应用前景极具优势。

5 结束语

为提高我国在先进封装技术领域的自主研发创新能力,建议针对半导体芯片产业链对高质量、高可靠性先进封装键合的迫切需求,开展晶圆级同质/异质封装键合基础理论及关键技术研究,重点探索突破封装键合的界面理论与工艺优化方法、复杂精密晶圆级封装系统设计原理与关键技术、高动态高精度晶圆封装系统检测控制理论与技术、集束型封装复杂生产过程优化控制理论与技术等发展瓶颈,构建晶圆级先进封装同质/异质键合理论与技术体系。

来源:原创 王成君 胡北辰 等 半导体封装工程师之家

半导体工程师半导体经验分享,半导体成果交流,半导体信息发布。半导体行业动态,半导体从业者职业规划,芯片工程师成长历程。234篇原创内容公众号

半导体工程师半导体经验分享,半导体成果交流,半导体信息发布。半导体行业动态,半导体从业者职业规划,芯片工程师成长历程。234篇原创内容公众号