在消费电子的浪潮中,电磁兼容性(EMC)是硬件工程师必须攻克的难关。从智能手机到智能家居设备,EMC设计直接影响产品的性能、可靠性和市场竞争力。随着设备小型化和高频化的趋势,电磁干扰(EMI)问题日益突出。据统计,全球消费电子市场预计到2030年将突破1.47万亿美元,而EMC合规性是产品上市前的必经之路。本文围绕PCB布局、屏蔽与接地、滤波与元件选择三个关键领域,提供实用建议和行业案例,助你在EMC设计中脱颖而出!

1. 理解消费电子中的EMC核心

电磁兼容性(EMC)是指设备在电磁环境中正常运行的能力,同时不产生或受到不可接受的电磁干扰(EMI)。在消费电子领域,EMC设计至关重要,因为设备通常在密集的电磁环境中运行,如家庭中的Wi-Fi路由器、智能音箱和手机。

EMC的三大要素

干扰源:高频信号、开关电源或时钟电路是常见的干扰源。

传输途径:干扰通过传导(如电源线)或辐射(如电磁波)传播。

接收器:敏感电路(如模拟放大器)容易受到干扰影响。

消费电子的EMC挑战

消费电子设备因其独特特性面临以下挑战:

小型化。设备体积小,组件密集,增加了内部EMI风险。例如,智能手机的PCB面积通常小于100平方厘米,却需集成多种高频模块。

高频环境。现代设备常运行在GHz频率(如5G模块),WIFI等导致更强的辐射干扰。

法规要求。产品需符合FCC Part 15(美国)或EN55032(欧洲)等标准,未能通过可能导致数百万的整改成本。

在高速逻辑电路里,EMI问题特别脆弱,原因很多,比如

1、电源与地线的阻抗随频率增加而增加,公共阻抗耦合的发生比较频繁;

2、信号频率较高,通过寄生电容耦合到步线较有效,串扰发生更容易;

3、信号回路尺寸与时钟频率及其谐波的波长相比拟,辐射更加明显;

4、引起信号线路反射的阻抗不匹配问题。

苹果iPhone通过精密的EMC设计确保其复杂硬件(如A系列芯片和5G模块)在紧凑空间内无干扰运行。苹果采用屏蔽、接地和滤波技术,并进行严格的EMC测试,确保产品符合全球标准。

2. 优化PCB布局

印刷电路板(PCB)是硬件系统的载体,同时也是EMI的主要来源之一,合理的布局和布线设计能显著降低干扰风险。以下是消费电子PCB设计的EMC最佳实践。

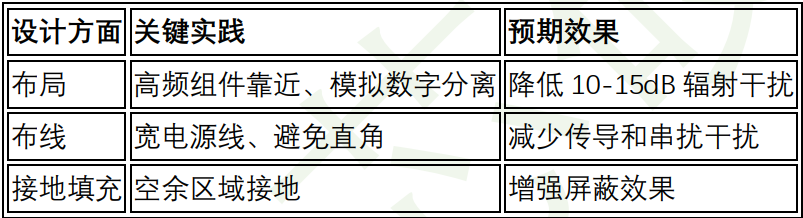

布局原则要求高频组件靠近放置。将晶振和处理器等高频组件尽量靠近,缩短迹线长度以减少环路面积。例如,将晶振与处理器间距控制在5mm以内,可将辐射干扰降低约10dB。模拟与数字电路分离,即将模拟和数字电路分区,防止数字噪声干扰模拟信号。使用接地平面隔离两区域效果更佳。还有电源与地平面设计,比如在多层板中,分配整层作为电源和地平面,提供低阻抗路径,降低EMI。

布线技巧中电源与地线优化,要求电源和地线尽量宽(如1mm以上),并在多层板中各占一面,减少阻抗。在一款30W USB-C充电器设计中,宽电源线将传导干扰从40dBμV降至30dBμV。同时减少环路面积,比如信号线与其回流路径靠近布线,环路面积越小,辐射越低。例如,差分信号线间距控制在0.2mm以内可有效降低串扰。还要避免直角布线,设计中高频信号线避免90度转角,使用45度或圆弧转角以减少信号反射。最后是关键信号保护,如时钟线和复位线靠近地回线布线,或添加专用回流路径,减少干扰。

在索尼PlayStation设计中,工程师采用先进的PCB设计技术,通过优化组件布局和布线,结合全面屏蔽和冷却系统,将辐射干扰控制在35dBμV以下,顺利通过FCC认证。

尽早测试PCB样板的EMI性能,尽早发现问题。

3. 屏蔽与接地构建防护壁垒

屏蔽和接地是控制EMI的基石,在消费电子的紧凑设计中尤为重要,因为很多设计中没有多余的空间优化。

屏蔽类型如高频干扰(>1MHz)主要靠反射屏蔽,使用高电导率材料(如铜)。低频磁场(<1MHz)需吸收屏蔽,使用高磁导率材料(如镀锌铁)。屏蔽设计要确保屏蔽体闭合并接地,缝隙尺寸小于最小波长的1/20。例如,5GHz信号的波长约为60mm,缝隙应小于3mm。在变压器、传感器和DC/DC模块常需屏蔽以防止磁耦合干扰。

接地策略是频率分级接地,如低于300kHz采用单点接地,避免地环路;高于300kHz使用多点接地,提供低阻抗路径。其次是电缆屏蔽接地,在电缆长度小于0.15λ时,输出端单点接地;长电缆每0.05-0.1λ接地一次。例如,2.4GHz Wi-Fi信号(波长约125mm)需每6-12mm接地。还有射频电路接地,要求接地线尽量短,优先使用扁平铜编织带,避免λ/4长度(易形成天线效应)。

屏蔽效能 SE(dB)=反射损耗 R(dB)+吸收损耗 A(dB)

高频射频屏蔽的关键是反射,吸收是低频磁场屏蔽的关键机理。

4. 滤波与元件选择来消除噪声

滤波和元件选择是EMC设计的最后一道防线,通过抑制高频噪声确保设备稳定运行。

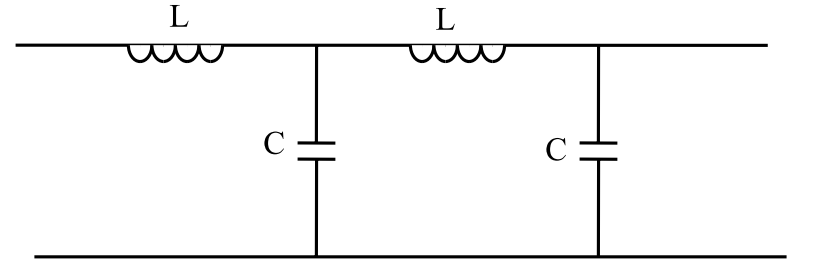

比如电源滤波中,在电源输入端使用EMI滤波器,阻止外部噪声进入和内部噪声外泄。π型滤波器因其优异的通带到阻带过渡性能,常用于消费电子。还有信号线滤波,在对外接口信号线添加滤波器(如LC滤波器),阻断高频噪声。例如,USB接口滤波可将差模干扰降低约20dB。

元件选择主要是以下三类,首先是去耦电容,在芯片电源引脚附近放置1-100nF去耦电容,滤除高频噪声。电容引线电感需最小化,建议使用四芯电容提高谐振频率。其次是铁氧体磁珠,在电源和信号线上使用铁氧体磁珠,抑制高频噪声。例如,Murata的BLM系列磁珠可将1GHz以上噪声衰减30dB。最后是电容选择,根据公式Cmin≈ΔIΔt/ΔVmax选择电容值,ΔVmax通常取电源电压的2%。例如,1A电流、10ns切换时间、0.1V噪声限值需至少100nF电容。

比如在Fitbit可穿戴设备通过集成小型化滤波器和铁氧体磁珠,确保设备在密集电磁环境中(如靠近手机)稳定运行。其设计将传导干扰控制在25dBμV以下,符合EN55032 Class B标准(In Compliance Magazine, 2025)。

结语

单板的干扰抑制涉及的面很广,从传输线的阻抗匹配到元器件的 EMC 控制,从生产工艺到扎线方法,从编码技术到软件抗干扰等,EMC设计是确保产品性能和合规性的关键。通过优化PCB布局、实施有效屏蔽与接地、选择合适的滤波器和元件,工程师可以打造无干扰、高可靠性的设备。苹果iPhone、索尼PlayStation和Fitbit的成功案例表明,EMC设计不仅是法规要求,更是提升用户体验的利器。本规范只简绍 EMC 的主要原则与结论,为硬件工程师们在开发设计中抛砖引玉。

ESD笔试核心题目详解-56期在硬件设计领域,电磁兼容性(EMC)和静电放电(ESD)防护能力直接决定产品的可靠性与合规性,也是企业筛选工程师的核心考察点。本文结合高频面试题与工程案例,助你系统掌握设计要点与解题逻辑。

ESD的保护路径和作用机理如下

电路板的对外接口部分,常用的与防护设计相关的器件种类有:

TVS管

压敏电阻

气体放电管

ESD是如何起作用的详细图示

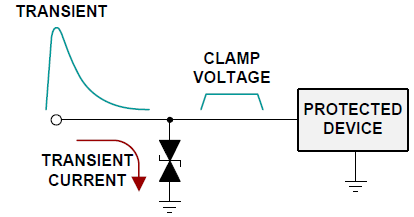

FIGURE 1、 TVS SHUNTS PROTECTED DEVICE DURING TRANSIENTS

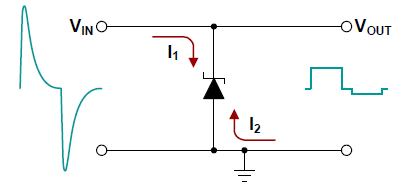

单向TVS Devices

The TVS acts in avalanche(雪崩) mode as the transient current I1 flows、

FIGURE 2、 CLAMPING ACTION OF A UNIDIRECTIONAL TVS

一、基础概念辨析:EMC、EMI、EMS与ESD

EMC(电磁兼容性)

定义:设备在电磁环境中正常工作,且不对其他设备产生不可接受干扰的能力。

组成:包含EMI(电磁干扰) 和 EMS(电磁抗扰度) 两方面。

关键指标:传导发射(CE)、辐射发射(RE)、静电抗扰度(ESD)等。

ESD(静电放电)

本质:静电荷瞬间释放(如人体触摸设备),峰值电压可达数万伏,频谱覆盖数百MHz至数GHz。

危害:导致芯片栅氧击穿、信号锁存、系统复位甚至永久损坏。

1、电磁干扰的三要素是什么?

电磁干扰源、干扰传播路径和干扰敏感设备。

2、请列举三种典型的ESD 模型。

人体模型(HBM)、机器模型(MM)、带电器件模型(CDM)。

3、请简述TVS 瞬态电压抑制二极管的工作原理。

当TVS 上的电压超过一定幅度时,器件迅速导通,从而将浪涌能量泄放掉,并将浪涌电压限制在一定的幅度。

4、请问为何手持便携电子产品,需要在众多输入输出接口加 ESD 器件?您认为选择 ESD 元件的时候需要注意哪些参数?

如果一个时钟线加了 ESD 器件之后接口工作不正常,把 ESD 器件去掉之后却能正常工作,您认为是什么原因,应该如何重 新选择ESD 器件?

手持设备,众多输入输出接口均可能受到静电放电的损害,所以要加ESD 保护器件。ESD 元件的选择需要注意三个参数:

正常工作电压、嵌位电压和等效电容。如果等效电容过大,会影响信号的工作频率,所以需要根据信号最大工作频率来选 择ESD 器件的等效电容。

5. 新手硬件工程师在EMC/ESD设计中容易犯的错误包括:

"在ESD设计中,为什么有时加了TVS二极管后接口工作不正常?"

可能的原因包括:

TVS二极管的结电容过大,影响信号完整性

接地阻抗过高,导致钳位电压失效

保护器件布局不合理,未能有效吸收ESD能量

解决方法是:选择低电容TVS二极管、优化接地设计、调整保护器件位置。在面试中,应结合具体场景分析问题,并提供可行的解决方案。

二、ESD模型与防护设计

静电放电(ESD)保护是硬件设计中的关键环节,尤其是手持设备和接口电路。面试中常会考察对ESD模型的理解及其应用:

"请列举三种典型的ESD模型并简要说明其区别"

三种典型模型是人体模型(HBM)、机器模型(MM)和带电器件模型(CDM)。它们的区别在于放电电流大小、持续时间和适用场景:

ESD模型

放电电流

持续时间

典型电压

适用场景

HBM(人体模型)

0.5-8A

~100ns

1-8kV

手持设备、人工操作

MM(机器模型)

~20A

~30ns

200-500V

自动化产线

CDM(带电器件模型)

~10A

~0.2-0.4ns

500-1500V

自动化测试、芯片封装

在回答时,应强调不同模型的放电特性与实际应用的对应关系,如HBM适用于人工操作场景,而CDM更适用于自动化产线环境。

"TVS二极管选型时需要关注哪些关键参数?"

TVS二极管选型需关注三个关键参数:**工作电压(VRWM)、最大钳位电压(VC(max))和结电容(C)。**其中,结电容很容易被新手忽略。工作电压应大于被保护电路的最大工作电压;最大钳位电压需小于被保护器件的损坏电压;**结电容则影响信号完整性,高频接口需选择低电容TVS。**此

外,还需考虑瞬态功率、响应时间等参数,以及温度变化对性能的影响。在面试中,可以结合具体应用场景(如USB接口、HDMI, 电源输入)说明参数选择的依据。

题目:某芯片HBM模型ESD阈值仅2kV(要求4kV),分析原因及改进措施

原因分析:

保护电路未优先导通(RC触发延时不足)

电流路径阻抗高(如TVS管接地不良);

敏感信号未串联限流电阻。

改进措施:

在I/O口串联100-500Ω电阻限制峰值电流;

优化TVS布局:靠近接口,接地引脚最短化;

检查电源/地平面完整性,确保低阻抗泄放路径。

题目:双层PCB无独立GND层,TVS防护ESD需注意什么?

核心难点:回流路径不完整导致能量无法泄放。

设计策略:在TVS接地端附近多点接地至金属外壳(降低接地阻抗);

敏感信号(如RESET)增加RC滤波(典型值:10kΩ+100pF)

避免TVS与受保护器件间走线过长(>5mm)。

题目:TVS二极管选型

题目:某USB接口需防浪涌保护,选择TVS二极管参数要求。

关键参数:击穿电压V_BR需高于工作电压(USB 5V):选V_BR=6.8V

脉冲功率P_P≥1500W(8/20μs脉冲)

响应时间<1ps(确保快速钳位)

型号推荐:SMBJ5.0A(击穿电压5V,钳位电压8V,P_P=1300W)

答案:推荐SMBJ5.0A型号,击穿电压5V,钳位电压8V。

ESD防护设计失败案例

真题:某芯片HBM模型ESD测试仅2kV(要求4kV),分析原因及改进措施。

根因:PCB布局中ESD防护二极管距离IO端口过远(>5mm),导致泄放路径阻抗过高。

改进方案:在IO端口就近添加TVS管(如SMAJ5.0A);

优化接地设计,采用网格状地平面降低阻抗。

三、工程级设计技巧与整改案例

1. 电容选型:ESD防护中的“疏”策略

案例:车载产品Pin脚ESD ±4kV测试失败,增加10nF电容后通过

原理:ESD能量集中于前30ns(频谱峰值50MHz),10nF电容在55MHz处阻抗最低,且未超过自谐振频率(27nF/33nF此时呈感性)

误区:盲目增大容值可能引发LC谐振,反而加剧EMI。

2. 电阻在ESD中的三重作用

限流:串联电阻降低峰值电流(例:I/O口加200Ω电阻);

延时:RC网络为TVS争取触发时间(数百ps级);

隔离:高阻值电阻(≥10kΩ)保护模拟电路(如PLL滤波器)。

3、请问RoHS 指令限制在电子电气设备中使用哪六种有害物质?

限制使用铅、汞、镉、六价铬、多溴联苯(PBB)和多溴二苯醚(PBDE)等六种有害物质。

4、ESD保护电路设计中,TVS二极管与电容并联的目的是什么?

在ESD保护电路中,TVS二极管与小电容并联的目的是:

小电容(如0.1μF)提供高频去耦,降低TVS的寄生电感影响

减小整体等效电容,避免对信号完整性造成过大影响

提高保护电路的响应速度,特别是在CDM等快速放电模型下

在面试中,应结合ESD模型的特性(如HBM、CDM的放电波形差异)说明这种设计的合理性。

题目5: 简述在PCB设计中,常用的降低EMI(电磁干扰)和提高EMC(电磁兼容性)的措施有哪些?请列举至少4条。

考察点: EMC/EMI原理、PCB布局布线、接地、滤波、屏蔽等。

详细分析:

EMI(Electromagnetic Interference): 指电子设备在运行过程中产生的不希望的电磁能量,干扰其他设备正常工作或自身正常工作。

EMC(Electromagnetic Compatibility): 指电子设备在电磁环境中能正常工作,且不对该环境中其他设备产生无法忍受的电磁干扰的能力。

PCB设计中降低EMI/提高EMC的措施:

1. 良好的接地设计:

地平面(Ground Plane): 使用连续、完整的地平面(特别是多层板),为信号提供低阻抗的回流路径,减小共模干扰。

单点接地或多点接地: 根据频率和电流大小选择合适的接地策略,避免地环路。

数字地与模拟地隔离: 对于混合信号板,应将数字地和模拟地在一点连接,并通过磁珠或小电阻隔离,避免数字噪声耦合到模拟电路。

2. 优化电源去耦:

去耦电容: 在IC的电源引脚附近放置大小合适的去耦电容(通常是陶瓷电容),提供低阻抗的局部电源,抑制电源噪声,缩短电流环路面积。高频电容靠近芯片,低频电容远离。

电源平面: 使用连续的电源平面,提供稳定的电源分配。

3. 信号路径优化:

最短路径原则: 信号线和回流路径应尽可能短,减少环路面积,降低辐射。

阻抗匹配: 对于高速信号线,进行阻抗匹配,减少信号反射,提高信号完整性。

差分信号: 使用差分信号对,利用共模抑制能力,降低共模噪声。

避免锐角走线和直角弯: 避免在高速线路上出现,减少阻抗不连续。

4. 滤波与屏蔽:

I/O接口滤波: 在板卡的输入/输出接口处使用共模扼流圈、差模电感、TVS管、RC滤波等,抑制外部干扰进入和内部干扰传出。

屏蔽: 对于敏感电路或高辐射源,可以使用金属屏蔽罩,阻挡电磁波的辐射或耦合。

5. 元件布局:

功能模块分区: 将模拟电路、数字电路、电源电路、高速电路等功能模块分区放置,减少相互干扰。

敏感元件远离噪声源: 将高频晶振、大功率开关器件等噪声源远离敏感电路。

电源平面下的过孔: 避免高速信号线在电源平面上打孔,因为这会破坏电源平面的完整性。

四、备考建议与总结

理论基础:熟记ESD模型(HBM/CDM/MM)及测试标准(IEC 61000-4-2);理解信号回流路径与环路面积控制原则。

设计工具:利用插入损耗仿真工具(如Murata SimSurfing)优化电容选型;掌握TLP测试图分析ESD器件特性

EMC/ESD设计能力=理论基础×工程经验×系统思维。真正的高手,既要懂“电容电阻的微观选型”,也要会“层叠结构的宏观把控”。建议结合我此前分享的标准文档(如JESD22-A115)和EDA工具实操深化理解,逐步构建可落地的设计闭环。