上周帮同事排查一款产品时,连续烧了 3 块样板才找到问题根源:他把ESD 防护二极管的方向画反了!这种用于电源接口的 TVS 二极管,就像电路里的“单向防洪闸”,正常情况下能吸收静电冲击保护芯片,反接后却会变成“导线”,通电瞬间就被击穿,不仅电源报废,还会连带烧毁与之相连的主控芯片。

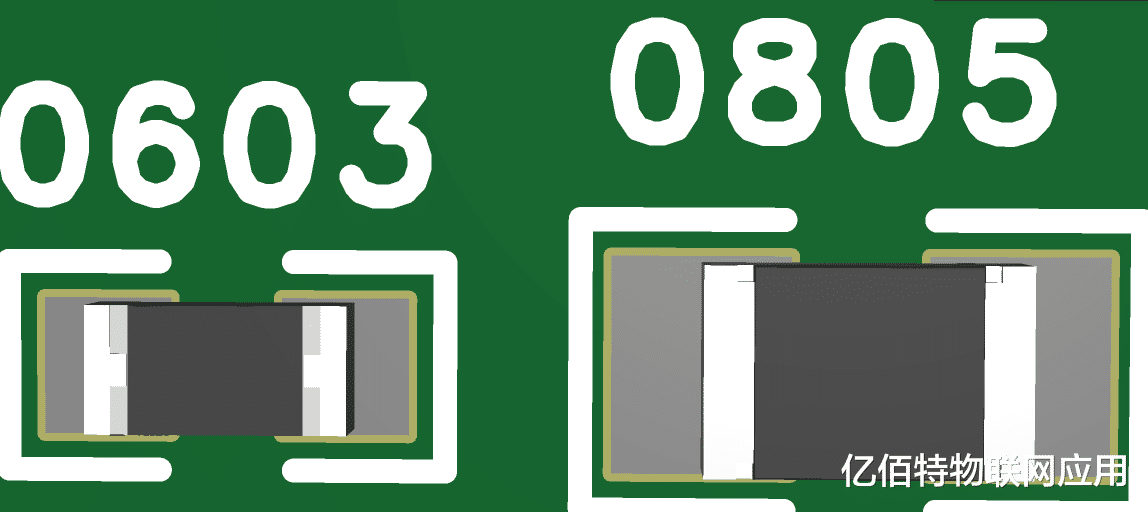

更隐蔽的是封装匹配问题。今年前段时间,我曾将 0603 电阻的封装误选为0805,虽然原理图上只是数字差异,但实际生产时,贴片机的吸嘴根本无法精准定位,导致20%的电阻贴偏、虚焊,后期返工花了整整3天。

我的避坑技巧:

1.极性元件双重标注:所有二极管、电解电容、集成 IC 在原理图中标注“+/-”或“PIN1”符号,同时在元件位号旁备注型号规格(如“D1: SMAJ6.5CA双向TVS”),避免选错型号。

2.3D 视图强制核对:调用封装库后必须切换至 3D 视图检查,重点核对焊盘间距、元件高度是否符合结构设计要求。下图是0603与0805电阻的3D封装对比,可见两者的焊盘间距差异明显:

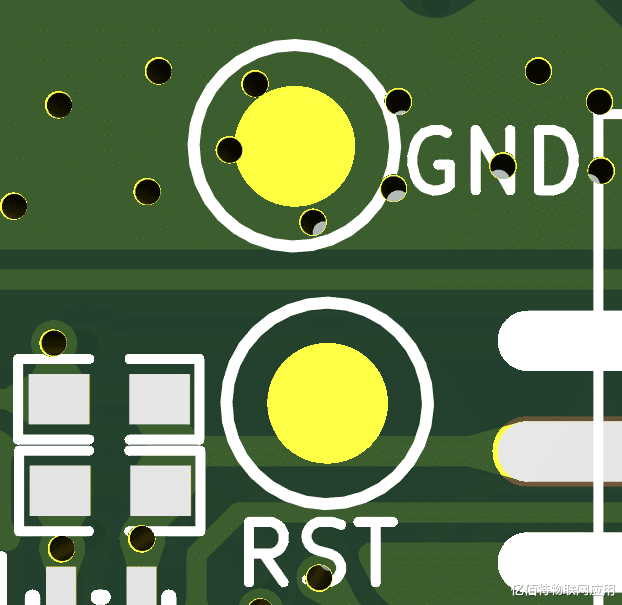

1.测试点标准化设计:关键信号(时钟线、复位线、电源轨)旁预留直径≥0.8mm的测试点,旁边写上丝印方便调试时快速定位,下图是单片机复位线和地的测试点:

年初接手一个工业控制板项目时,反馈设备在车间环境中频繁死机。拆开外壳测量发现,电源地与信号地之间的电压差居然有 200mV—— 这意味着两种接地网络的干扰已经严重影响信号传输。追查原因才发现,前一版设计将电源地和信号地直接合并布线,就像把家里的电线和网线缠成一团,电机启动产生的大电流干扰直接让CPU “误判指令”。

接地设计的核心是 “隔离干扰源与敏感源”。在低频电路(<1MHz)中,单点接地是最可靠的方案,能有效避免共地阻抗耦合产生的干扰。某汽车电子项目中,工程师采用串联单点接地导致音响系统出现杂音,后来改为并联单点接地后,干扰完全消除。

正确做法:

•采用分级单点接地:将电路分为模拟区、数字区、功率区,各区独立接地,最后通过一个公共接地点连接到电源地。下图是典型的单点接地图:

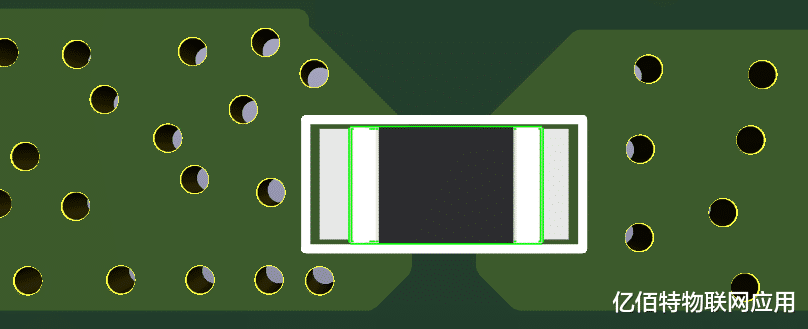

•大电流走线强化设计:电源走线按 “电流= 1A对应1mm线宽”的标准设计,如5V/2A的电源回路需≥2mm线宽,同时在走线拐角处采用45°角或圆弧过渡,避免尖端放电产生干扰。

•敏感元件隔离防护:晶振、ADC 芯片等敏感元件周围铺设“保护地环”,与功率器件(如MOS管、继电器)的距离保持≥5mm,必要时使用接地屏蔽槽隔离。

三、量产阶段:别忽略 “工艺兼容性”最惨痛的教训发生在一年前:为节省每块板 2 元的成本,我选用了一款非标间距的TypecUSB 连接器,虽然样品测试一切正常,但量产时问题彻底爆发——贴片厂的钢网无法匹配其特殊焊盘,贴片机识别率不到50%,只能安排工人手工焊接。更麻烦的是,手工焊接温度难以控制,导致10%的连接器引脚虚焊,最终不仅没省钱,反而多花了5万元返工费。

量产阶段的核心是 “与制造工艺匹配”,任何脱离生产实际的设计都是纸上谈兵。根据PCB厂的经验数据,0402以下的超小元件、间距≤0.5mm的QFP芯片,都需要提前进行工艺可行性验证。

量产前必做 3 件事:

1.钢网文件联合评审:将 PCB 文件与钢网文件同步发给PCB厂和贴片厂,三方共同确认焊盘开口尺寸(通常为焊盘宽度的70%-80%)、避让区域,避免出现“焊盘太小漏锡”“开口过大连锡”等问题。

2.工艺测试样板验证:制作 5-10 块工艺测试板,完全模拟量产流程进行贴片、焊接,重点检查0402以下元件的贴装良率、BGA芯片的焊点质量,测试数据需满足“贴装良率≥99.5%”“焊点合格率100%”。

3.供应链风险排查:用 BOM 表逐一核对元件的供货周期,冷门型号需确认至少2家替代供应商。